- 「MOSFETのゲートに信号入れるだけでしょ?なんで"駆動回路"がいるの?」

- 「抵抗1本でいいの?ICが必要なの?何がベストなの?」

- 「回路図を見るとNPNとPNPが並んでいる。これは何をしている?」

- 「スイッチング波形がなまって、MOSFETが異常発熱する…」

- ゲート駆動回路が必要な「物理的な理由」

- MOSFETのゲートは「コンデンサ」──だから電流が必要

- 抵抗1本の最小構成から、トーテムポール、ICまで5つの回路構成

- 各回路の「メリット・デメリット・使いどころ」

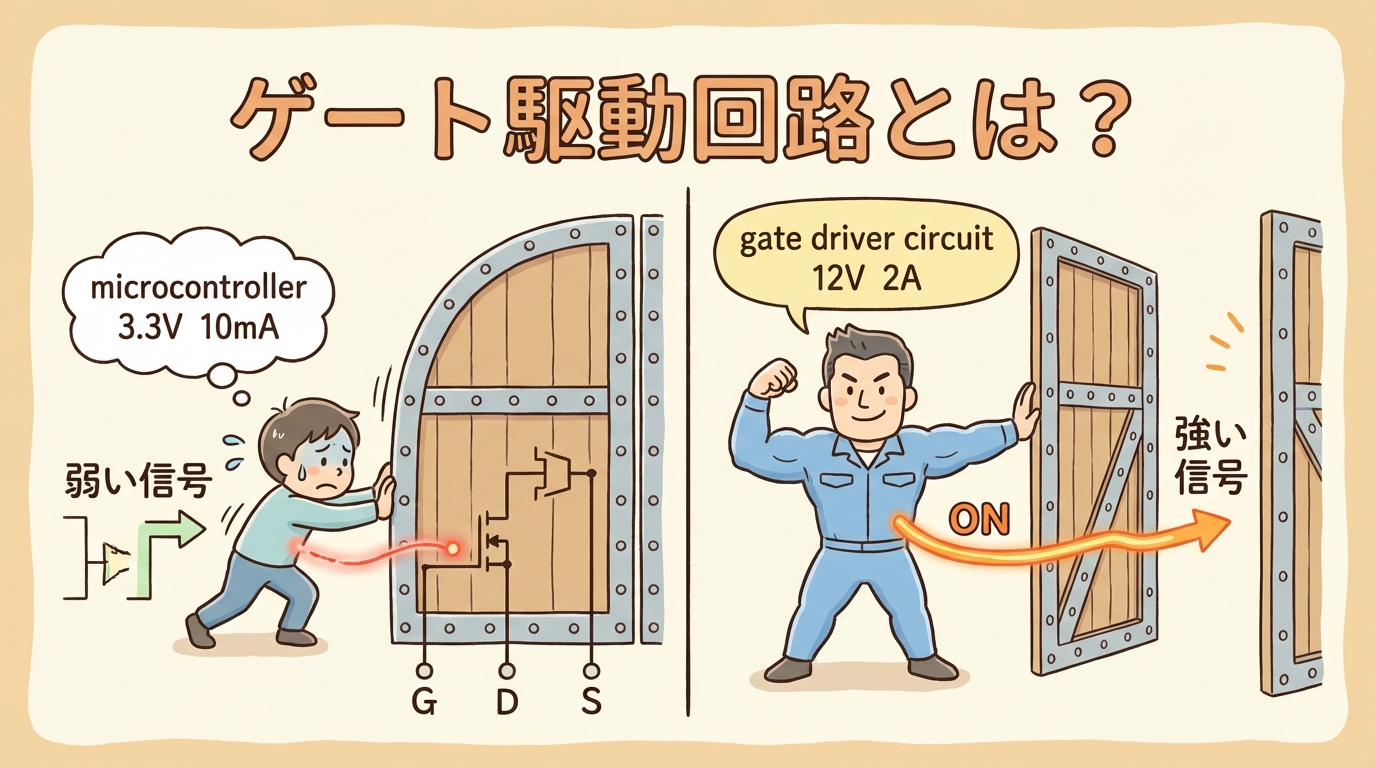

パワーエレクトロニクスの回路図を初めて見たとき、「MOSFETのゲートの周りに、やたらと部品がくっついているな…」と思ったことはありませんか?

あの「ゲートの周りの回路」こそが、ゲート駆動回路(ゲートドライブ回路)です。

MOSFETやIGBTは「電圧でON/OFFするスイッチ」──だったら、ゲートに電圧をかけるだけでいいはず。なのに、なぜわざわざ「駆動回路」が必要なのか?

その答えは、「MOSFETのゲートはコンデンサだから」です。この一言を理解すれば、ゲート駆動回路のすべてが腑に落ちます。この記事では、抵抗1本の最もシンプルな構成から、ゲートドライバICを使った本格的な構成まで、「なぜその回路が必要なのか」をイメージ重視で徹底解説します。

目次

- そもそもゲート駆動回路とは何か?──「スイッチを押す手」の役割

- なぜゲート駆動回路が必要なのか?──「コンデンサの充放電」という本質

- ゲート電荷(Qg)を理解する──「水をバケツに注ぐスピード」の問題

- ゲート駆動回路の5つの構成──シンプルな順に理解する

- 構成❶❷:抵抗だけの最小構成──最もシンプルだが限界がある

- 構成❸:NPN/PNPトーテムポール──「電流の壁」を突破する王道回路

- 構成❹:PMOS/NMOSトーテムポール──VBE降下をなくす進化形

- 構成❺:ゲートドライバIC──実務の標準解はこれ

- どの構成を選ぶか?──判断フローチャート

- 実務で気をつけるべき3つのポイント

- まとめ:ゲート駆動回路は「MOSFETを生かすも殺すもする裏方」

そもそもゲート駆動回路とは何か?──「スイッチを押す手」の役割

ゲート駆動回路とは、MOSFETやIGBTのゲートに適切な電圧・電流を供給して、素早く確実にON/OFFさせるための回路です。

家の照明スイッチで例えるなら、MOSFETは「スイッチ本体」、ゲート駆動回路は「スイッチを押す手」に相当します。スイッチがどれだけ優秀でも、押す手が弱ければ素早くパチッと切り替えられません。指先で恐る恐る触っていたら、接点がチャタリングを起こしてしまいます。

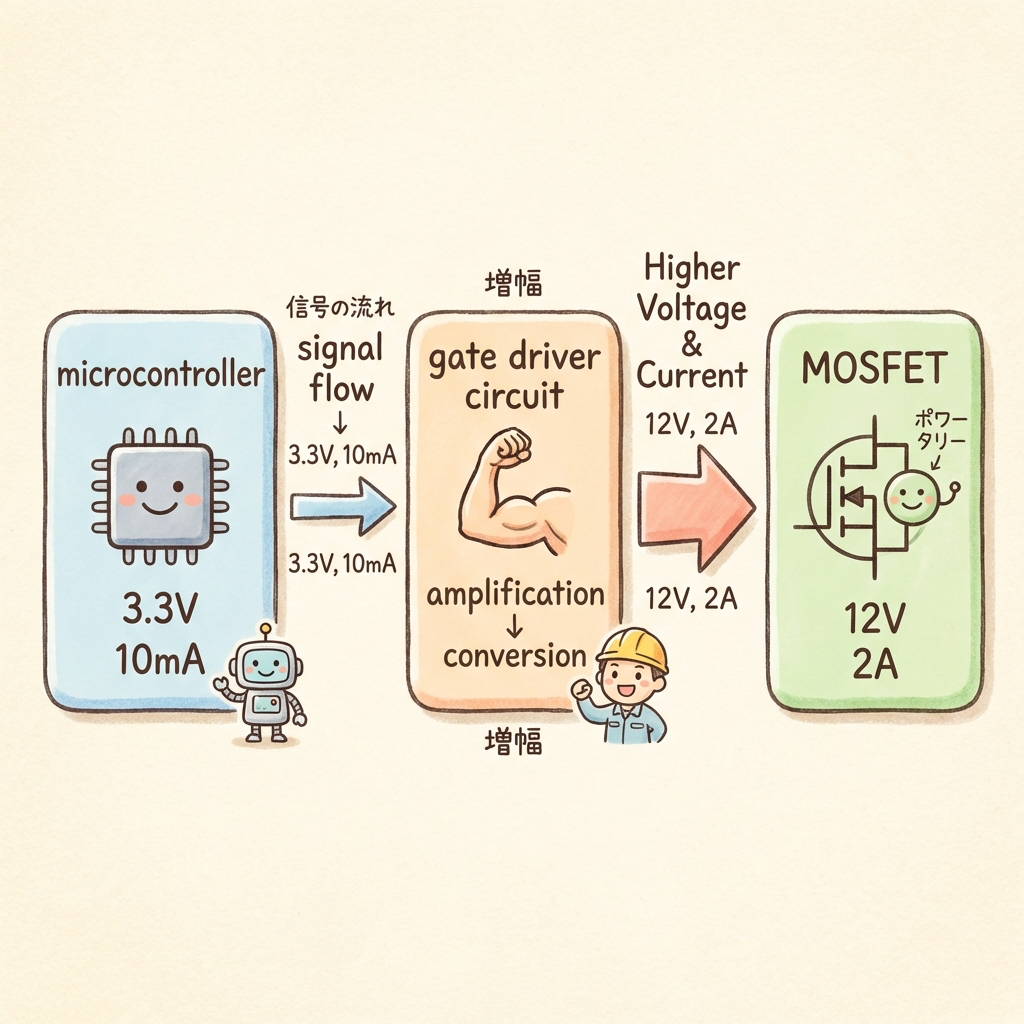

3.3V / 数mA

12V / 数A

つまりゲート駆動回路は、マイコンの「弱い信号」をMOSFETが動作できる「強い信号」に変換する、中間の増幅ステージです。構成は抵抗1本のシンプルなものから、専用ICを使った高機能なものまで様々ありますが、やっていることの本質は同じ──「ゲート容量を素早く充放電すること」です。

「MOSFETが壊れた」「異常発熱する」「ノイズが出る」──こうしたトラブルの原因を追っていくと、実はゲート駆動回路に問題があった、というケースは非常に多いです。主役のMOSFETばかり気にしがちですが、脇役のゲート駆動回路こそが安定動作のカギを握っています。

なぜゲート駆動回路が必要なのか?──「コンデンサの充放電」という本質

理由の核心:MOSFETのゲートは「コンデンサ」だから

MOSFETは「電圧制御デバイス」と呼ばれます。ゲート-ソース間に電圧(VGS)をかけるだけでONになる。だったら電圧さえかければいい──これは半分正解で、半分間違いです。

MOSFETのゲートは、構造的に金属-酸化膜-半導体(Metal-Oxide-Semiconductor)の積層になっています。これはまさにコンデンサの構造そのものです。

コンデンサ

金属板 ── 絶縁体 ── 金属板

電荷を蓄えないと電圧が上がらない

MOSFETのゲート

ゲート電極 ── 酸化膜 ── 半導体チャネル

電荷を注入しないとVGSが上がらない

コンデンサに電圧をかけるには、電荷を流し込む(=電流を流す)必要があります。しかもその電荷を一瞬で注入・引き抜きしなければ、MOSFETのスイッチングは遅くなります。

「MOSFETをONにする」 = 「ゲート容量を充電する」 = 「電流を流す」

「MOSFETをOFFにする」 = 「ゲート容量を放電する」 = 「電流を引き抜く」

「ゆっくり充電」するとどうなるか──スイッチング損失の地獄

「電流が少なくても、時間をかければ充電できるでしょ?」──たしかにその通りです。しかし、パワーエレクトロニクスの世界では「ゆっくりON/OFF」は命取りになります。

MOSFETがONとOFFの間を遷移している最中は、高電圧と大電流が同時にかかる状態です。これが「スイッチング損失」を生みます。工場のベルトコンベアに例えると、モーターが「回転中」か「停止中」なら問題ありませんが、「起動途中」の状態が長いほどモーターに負担がかかるのと同じです。

素早くON/OFF

遷移時間が短い

→ 損失が少ない

→ 発熱が少ない

→ 効率が高い

ゆっくりON/OFF

遷移時間が長い

→ 損失が大きい

→ 発熱が増える

→ 最悪、素子破壊

だからこそ、ゲート容量を「一瞬で充電・一瞬で放電」できる駆動回路が必要なのです。具体的な数値で確認してみましょう。

| 項目 | マイコンGPIO | MOSFETが求めるもの |

|---|---|---|

| 出力電圧 | 3.3V〜5V | 10〜15V |

| 出力電流(ピーク) | 10〜20mA | 0.5〜5A |

| 出力インピーダンス | 数十Ω〜数百Ω | 数Ω以下 |

マイコンの出力とMOSFETの要求を比べると、電圧で3〜5倍、電流に至っては100倍以上のギャップがあります。このギャップを埋めるのが、ゲート駆動回路の仕事です。

ゲート電荷(Qg)を理解する──「水をバケツに注ぐスピード」の問題

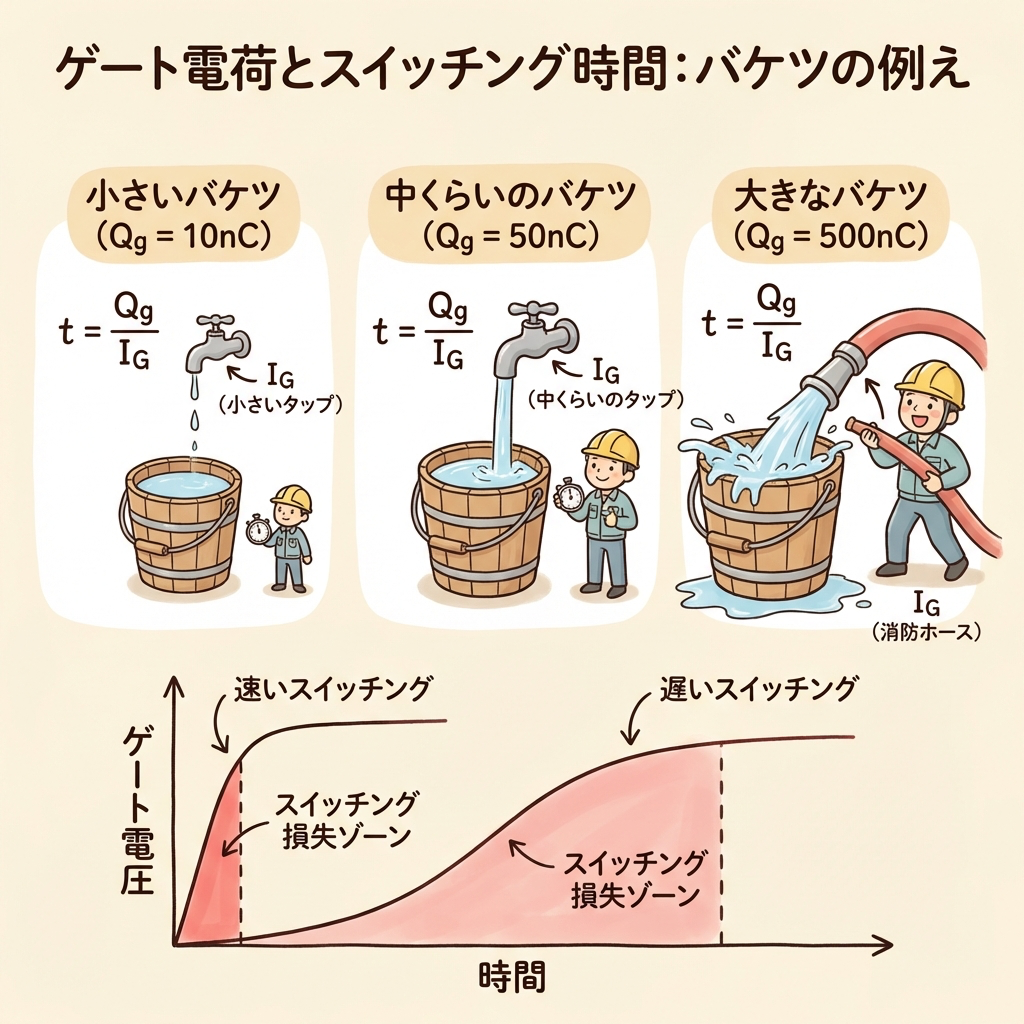

Qgとは「MOSFETをONにするために必要な電荷の総量」

MOSFETのデータシートには「Qg(ゲート総電荷量)」という値が記載されています。単位はnC(ナノクーロン)で、「このMOSFETをONにするために、ゲートに注入しなければならない電荷の量」を表します。

バケツに水を注ぐイメージで考えてみてください。

バケツの容量 = Qg

MOSFETのサイズが大きいほど

Qgも大きい(バケツが大きい)

水の勢い = 駆動電流

ゲート駆動回路が供給する電流

大きいほど素早く満タンになる

満タンまでの時間 = スイッチング時間

t = Qg ÷ IG

電流が大きいほど時間が短い

Qg = ゲート総電荷量 [nC]、IG = ゲート駆動電流 [A]、tsw = スイッチング時間 [ns]

具体例:Qg = 50nCのMOSFETを100nsでONしたい場合

計算してみましょう。必要な駆動電流は以下の通りです。

= 50nC ÷ 100ns

= 0.5A(500mA)

マイコンのGPIOが出せるのはせいぜい10〜20mA。必要な電流の1/25〜1/50しか流せません。これでは充電に2.5μs〜5μsかかり、100kHzのスイッチングでは毎サイクルの遷移時間が長すぎて、MOSFETが常に中途半端なON状態──つまり巨大な抵抗として発熱し続けることになります。

MOSFETのゲート駆動は「定常的に電流を流し続ける」必要はありません。ONの瞬間にパルス的に大電流を注入し、OFFの瞬間に大電流を引き抜くだけです。定常ON状態ではゲート電流はほぼゼロ。だからこそ「パルス的な大電流を供給できる能力」が重要なのです。

ゲート駆動回路の5つの構成──シンプルな順に理解する

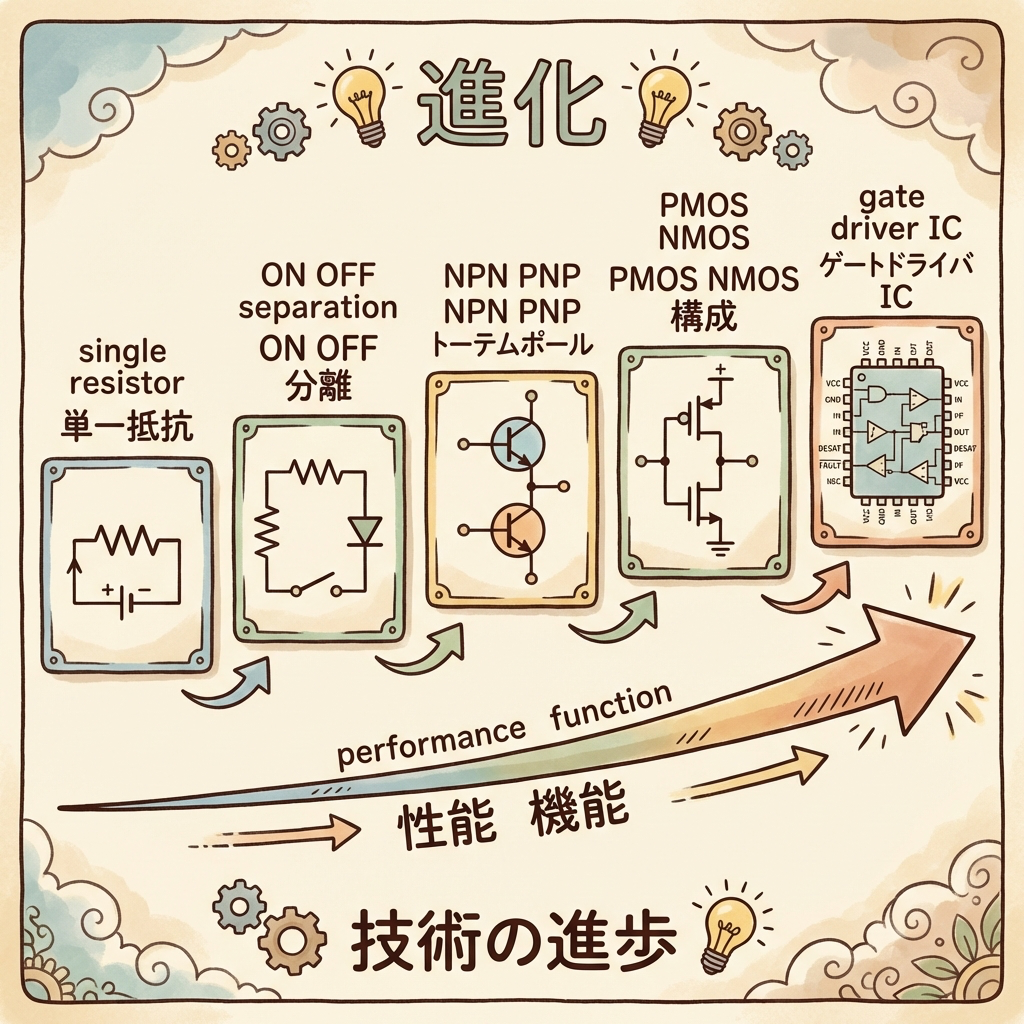

ゲート駆動回路は、目的も構成も様々ですが、基本的に「ゲート容量にどうやって電流を流し込むか(引き抜くか)」という1点だけを解決しようとしています。ここでは、シンプルな構成から順に5つのパターンを紹介します。

| 構成 | 部品数 | 駆動能力 | 主な用途 |

|---|---|---|---|

| ❶ 抵抗1本 | 1個 | 低 | 低速スイッチング、学習用 |

| ❷ ON/OFF個別抵抗 | 2〜3個 | 低〜中 | ON/OFF速度を個別に調整 |

| ❸ NPN/PNPトーテムポール | 3〜5個 | 中〜高 | ディスクリート高速駆動 |

| ❹ PMOS/NMOSトーテムポール | 3〜5個 | 中〜高 | 高速・低損失駆動 |

| ❺ ゲートドライバIC | 1個(+周辺部品) | 高 | 実務の標準。ハイサイド対応も |

それぞれ「なぜその構成が生まれたのか」を順番に見ていきましょう。

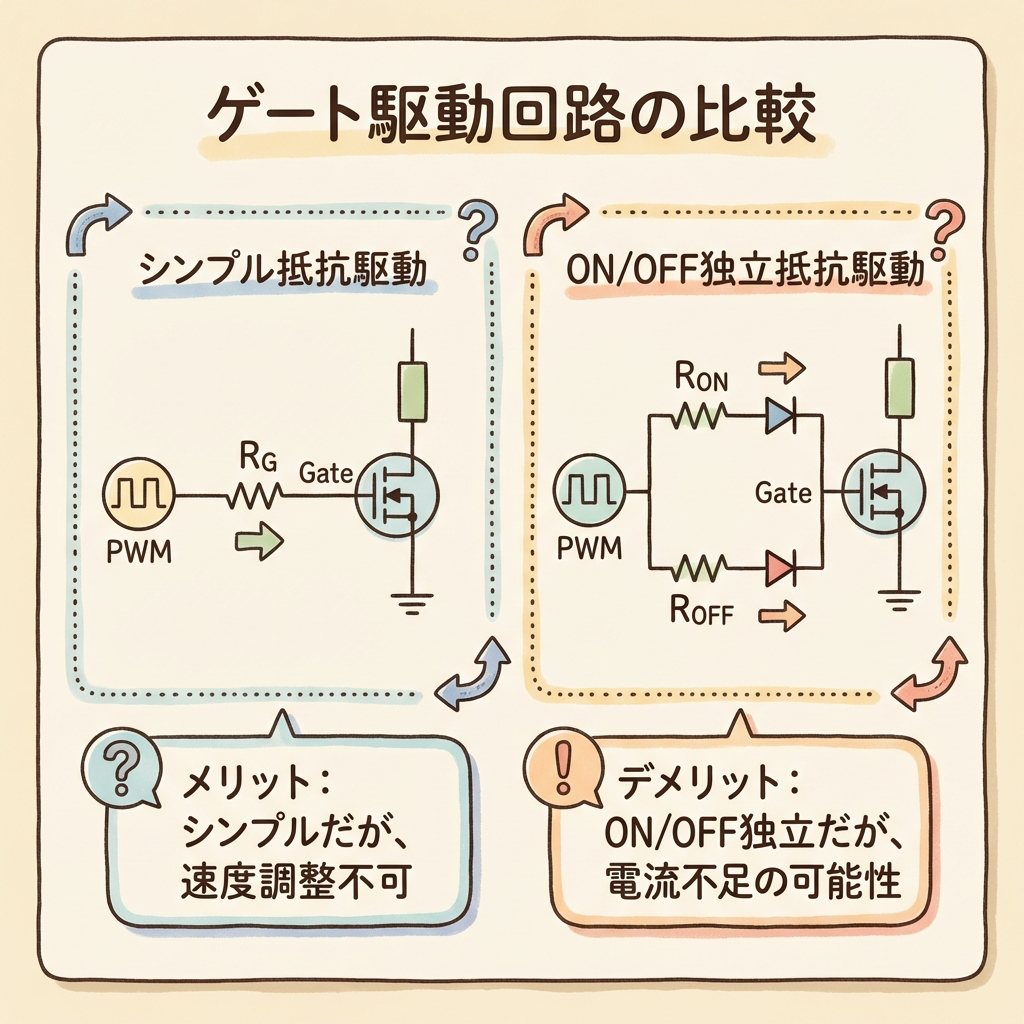

構成❶❷:抵抗だけの最小構成──最もシンプルだが限界がある

❶ 抵抗1本の基本形──「最低限のゲート駆動」

最もシンプルなゲート駆動回路は、PWMコントローラの出力とMOSFETのゲートの間に抵抗(RG)を1本入れるだけの構成です。

PWM出力 ──[ RG ]── Gate(G)

|

MOSFET

|

Source(S) ── GND

RGの役割は2つあります。

① 突入電流の制限:ゲート容量に瞬間的に流れるピーク電流を適度に制限し、PWMコントローラの出力を保護します。RGがないと、コントローラICに数Aのパルス電流が流れて破損する可能性があります。

② スイッチング速度の調整:RGが小さいほどスイッチングは速くなりますが、ノイズ(EMI)が増えます。RGが大きいほど穏やかですが、スイッチング損失が増えます。このトレードオフを調整するのがRGです。

この構成では、ONもOFFも同じ抵抗値で充放電することになります。「ONは速くしたいけどOFFはもっと速くしたい」といった要求に応えられません。また、駆動源(PWMコントローラ)の電流能力がそのまま上限になるため、大型MOSFETには力不足です。

❷ ON/OFF個別抵抗──ダイオードで充電と放電を分離する

構成❶の弱点を解決するために、ダイオードを追加してON用の抵抗(RON)とOFF用の抵抗(ROFF)を分離する方法があります。

PWM出力 ──┬──[ RON ]──▷|── Gate(G)

└──[ ROFF ]──|◁── Gate(G)

(▷| = 充電方向のダイオード、|◁ = 放電方向のダイオード)

これにより、ON時はRON経由でゆっくり充電(ノイズを抑制)、OFF時はROFF経由で素早く放電(スイッチング損失を低減)といった独立調整が可能になります。実務では「OFFを速くしたい」場合が多いため、ROFF < RON とする設計が一般的です。

ただし、ここまで紹介した構成❶❷は、あくまで駆動源自体の電流能力に依存しています。PWMコントローラの出力電流が足りなければ、抵抗をいくら小さくしてもスイッチングは速くなりません。この「電流能力の壁」を突破するのが、次に紹介する「トーテムポール回路」です。

ゲート抵抗の決め方|Qgから抵抗値を計算する設計手順 →

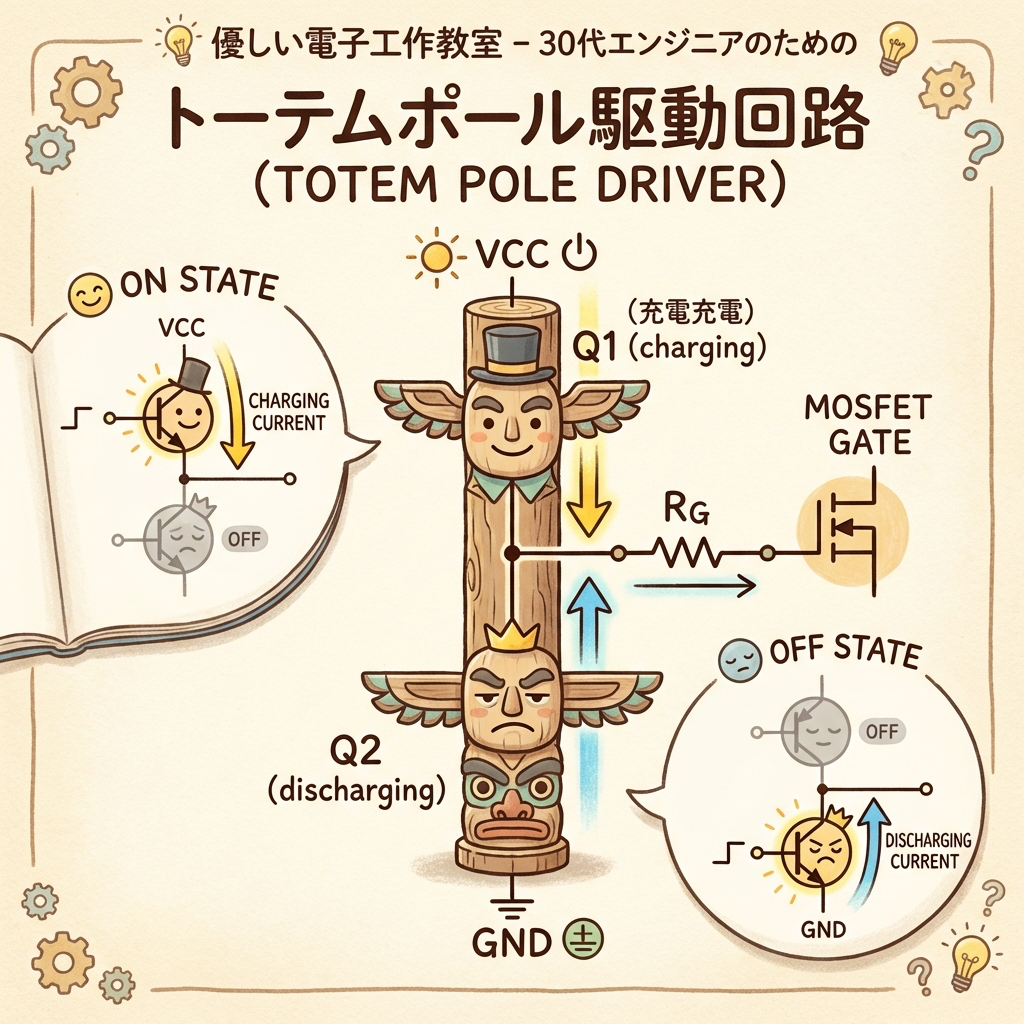

構成❸:NPN/PNPトーテムポール──「電流の壁」を突破する王道回路

トーテムポールとは?──「押す係」と「引く係」を分ける発想

ゲート駆動回路の世界で最も重要な回路構成が「トーテムポール(Totem-Pole)」です。名前の由来は、NPNトランジスタとPNPトランジスタを縦に積み上げた形がトーテムポール(柱状の彫刻)に似ていることから来ています。

この回路のアイデアはシンプルです。「充電専用のトランジスタ(押す係)」と「放電専用のトランジスタ(引く係)」を分担させることで、小さな制御信号から大きなゲート駆動電流を作り出します。

VCC(12V)

|

[NPN Q1] ← 充電係(ソース:電流を押し出す)

|

制御信号 ──┤ ├──[RG]── Gate

|

[PNP Q2] ← 放電係(シンク:電流を引き抜く)

|

GND

動作原理──「制御信号がHigh → NPN ON → ゲート充電」

制御信号がHighになると、NPN(Q1)がONします。VCCからQ1を通ってゲート容量に電流が流れ込み(ソース電流)、ゲート電圧が上昇してMOSFETがONになります。このときPNP(Q2)はOFFです。

制御信号がLowになると、PNP(Q2)がONします。ゲート容量に蓄えられた電荷がQ2を通ってGNDに流れ出し(シンク電流)、ゲート電圧が下降してMOSFETがOFFになります。このときNPN(Q1)はOFFです。

NPN・PNPトランジスタの電流増幅率(hFE)は通常50〜200程度です。つまり、制御信号から10mAを流すだけで、ゲートには0.5A〜2Aのピーク電流を供給できます。これが、PWMコントローラの数十mAから数Aのゲート駆動電流を生み出す「増幅」のメカニズムです。

トーテムポール回路の本質は「充電経路と放電経路を別のトランジスタで担当させる」ことです。これにより、充電時にはVCCからゲートへ、放電時にはゲートからGNDへ、それぞれ低インピーダンスの経路が確保されます。1本の抵抗で両方をまかなう構成❶❷とは、根本的に「電流の流れやすさ」が違うのです。

トーテムポールの注意点──VBE降下とクロスオーバー歪み

NPN/PNPトーテムポールには1つ弱点があります。バイポーラトランジスタのベース-エミッタ間には約0.6〜0.7Vの順方向電圧降下(VBE)があるため、ゲートに印加できる電圧はVCCよりも約0.7V低くなります。また、OFF時のゲート電位もGNDぴったりではなく約0.7Vになります。

さらに、NPN(Q1)がOFFしてからPNP(Q2)がONするまでの瞬間、両方がOFFになる区間が発生します(クロスオーバー歪み)。この間はゲートがハイインピーダンスになり、ノイズの影響を受けやすくなります。ゲート-ソース間に10kΩ程度の抵抗(RGS)を入れて、不定状態を防ぐのが定石です。

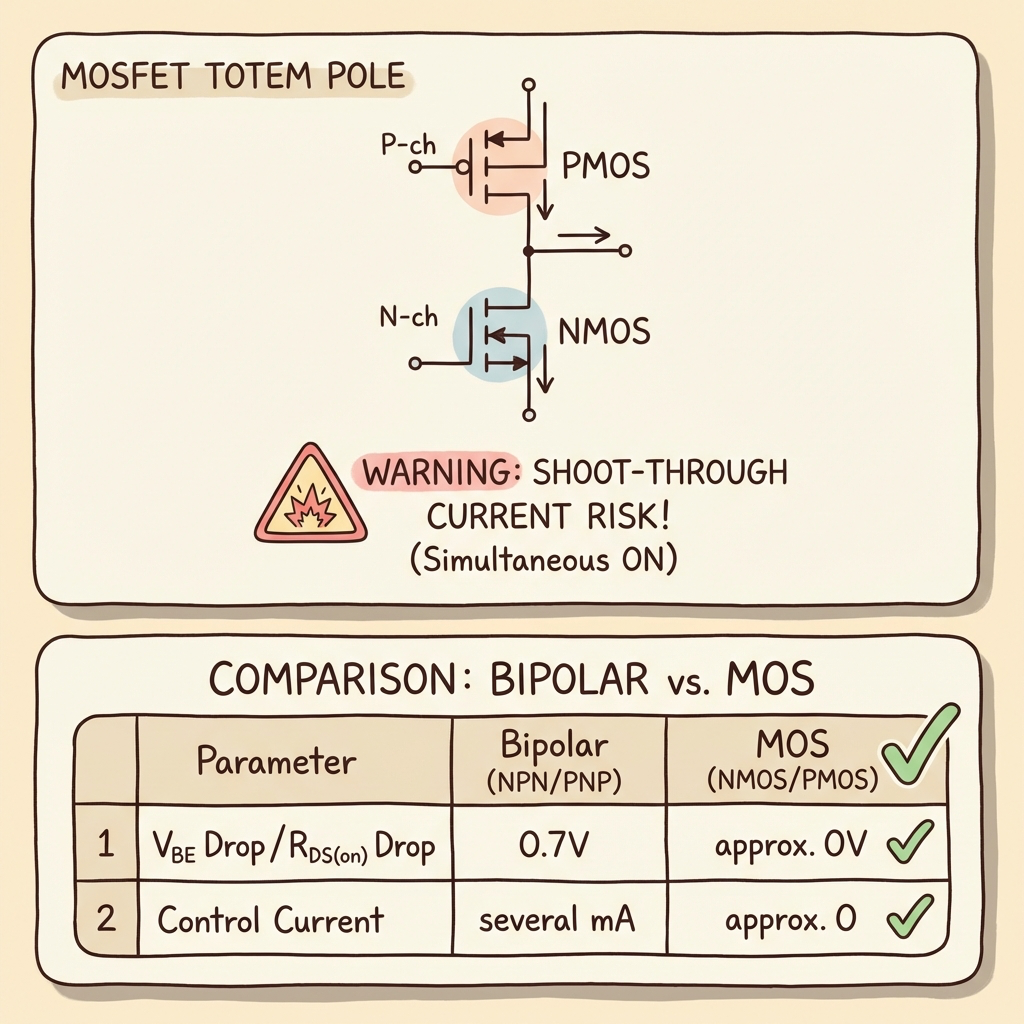

構成❹:PMOS/NMOSトーテムポール──VBE降下をなくす進化形

バイポーラの代わりにMOSFETを使う理由

NPN/PNPトーテムポールの弱点であった「VBE降下による電圧ロス」を解決するために、バイポーラトランジスタの代わりにPMOS(上側)とNMOS(下側)のMOSFETペアを使う構成があります。

VCC(12V)

|

[PMOS Q1] ← 充電係

|

制御信号 ──┤ ├──[RG]── Gate

|

[NMOS Q2] ← 放電係

|

GND

MOSFETはON時にはRDS(on)(数十mΩ〜数Ω)しか電圧降下しないため、ゲートにVCCのほぼフル電圧を印加でき、OFF時もほぼGNDまで引き下げられます。これが最大のメリットです。

| 比較項目 | NPN/PNP トーテムポール |

PMOS/NMOS トーテムポール |

|---|---|---|

| ON時のゲート電圧 | VCC − 0.7V | ≈ VCC |

| OFF時のゲート電圧 | ≈ 0.7V | ≈ 0V |

| 駆動電流 | 数A級 | 数A級 |

| 制御信号電流 | 数mA〜数十mA | ほぼゼロ |

| 貫通電流リスク | 低(VBEでギャップ) | やや高(要注意) |

PMOS/NMOS構成では、制御信号の遷移時にPMOSとNMOSが同時にONする瞬間が生じ、VCCからGNDへの貫通電流(シュートスルー電流)が流れるリスクがあります。実際のゲートドライバIC内部にはこの対策(デッドタイム挿入やアダプティブ制御)が組み込まれていますが、ディスクリートで組む場合は設計者が意識する必要があります。

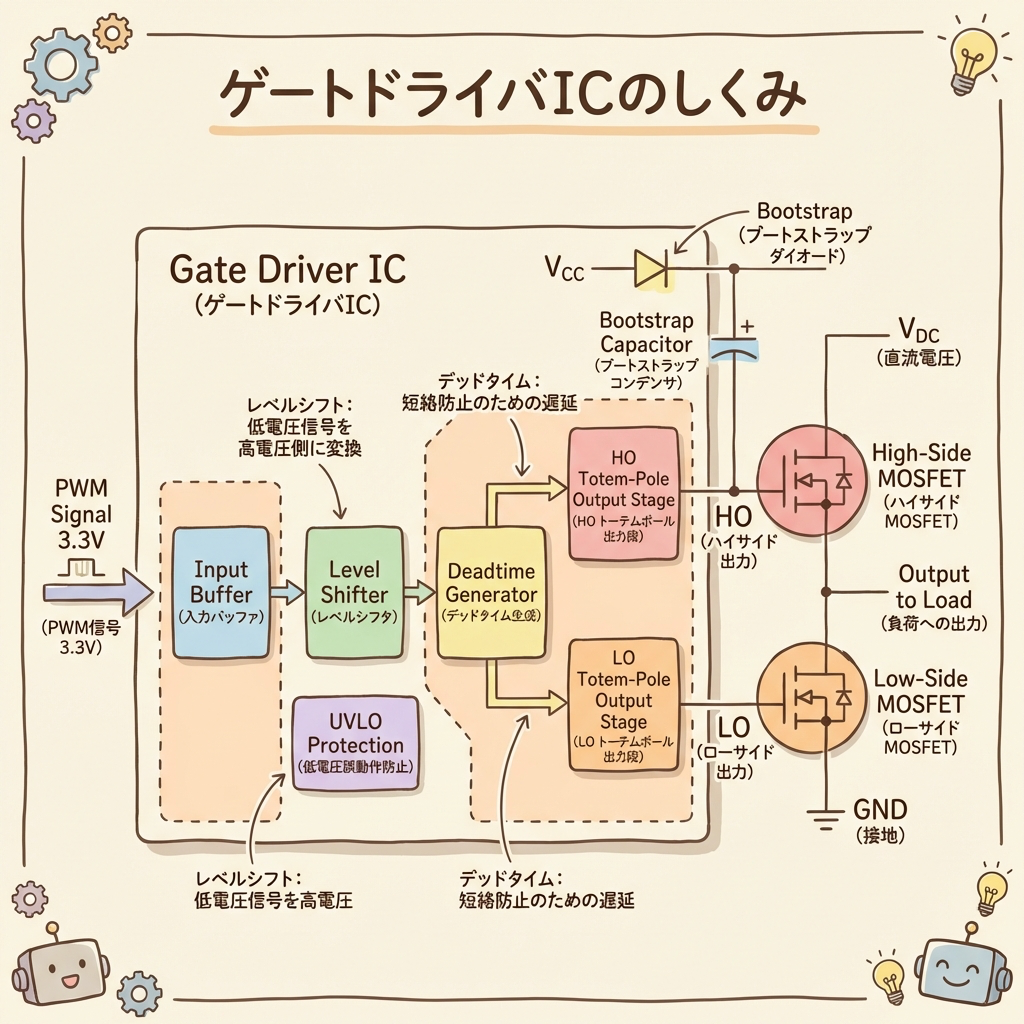

構成❺:ゲートドライバIC──実務の標準解はこれ

「トーテムポール + 保護回路 + ハイサイド駆動」をワンチップに

ここまで紹介した❶〜❹の回路は、いずれも「ローサイド駆動」──つまりMOSFETのソースがGNDに固定されている場合にしか対応できません。ハーフブリッジ回路やフルブリッジ回路で上側(ハイサイド)のMOSFETを駆動するには、さらに複雑な仕組みが必要になります。

そこで登場するのがゲートドライバICです。ゲートドライバICは、トーテムポール出力段に加えて、レベルシフト、ブートストラップ対応、デッドタイム生成、過電流保護、UVLO(低電圧ロックアウト)など、ゲート駆動に必要な機能を1つのICに統合したものです。

🏗️ ゲートドライバICの内部構造(概念図)

┌───────────────────────────────┐

│ ゲートドライバIC │

│ │

│ 入力バッファ → レベルシフタ │

│ ↓ │

│ デッドタイム生成回路 │

│ ↓ │

│ トーテムポール出力段 │──→ HO(ハイサイド出力)

│ トーテムポール出力段 │──→ LO(ローサイド出力)

│ │

│ UVLO / 保護回路 │

└───────────────────────────────┘

ゲートドライバICの主な種類

| 種類 | 構成 | ハイサイド | 主な用途 |

|---|---|---|---|

| ローサイド専用 | 1ch出力 | ✕ | 電流ブースト、簡単なスイッチ |

| ハーフブリッジ型 | HO + LO | ◯(ブートストラップ) | DC-DCコンバータ、モータ駆動 |

| 絶縁型 | 1ch(絶縁) | ◯(絶縁電源) | 高電圧インバータ、車載 |

| 3相ブリッジ型 | 6ch出力 | ◯ | 3相モータ駆動(BLDC等) |

実務では、よほど特殊な事情がない限りゲートドライバICを使うのが標準です。ディスクリートのトーテムポールで組むのは、コスト感度が極めて高い量産品か、学習目的くらいです。ICなら数十円〜数百円で「保護回路まで込み」の高性能な駆動回路が手に入ります。

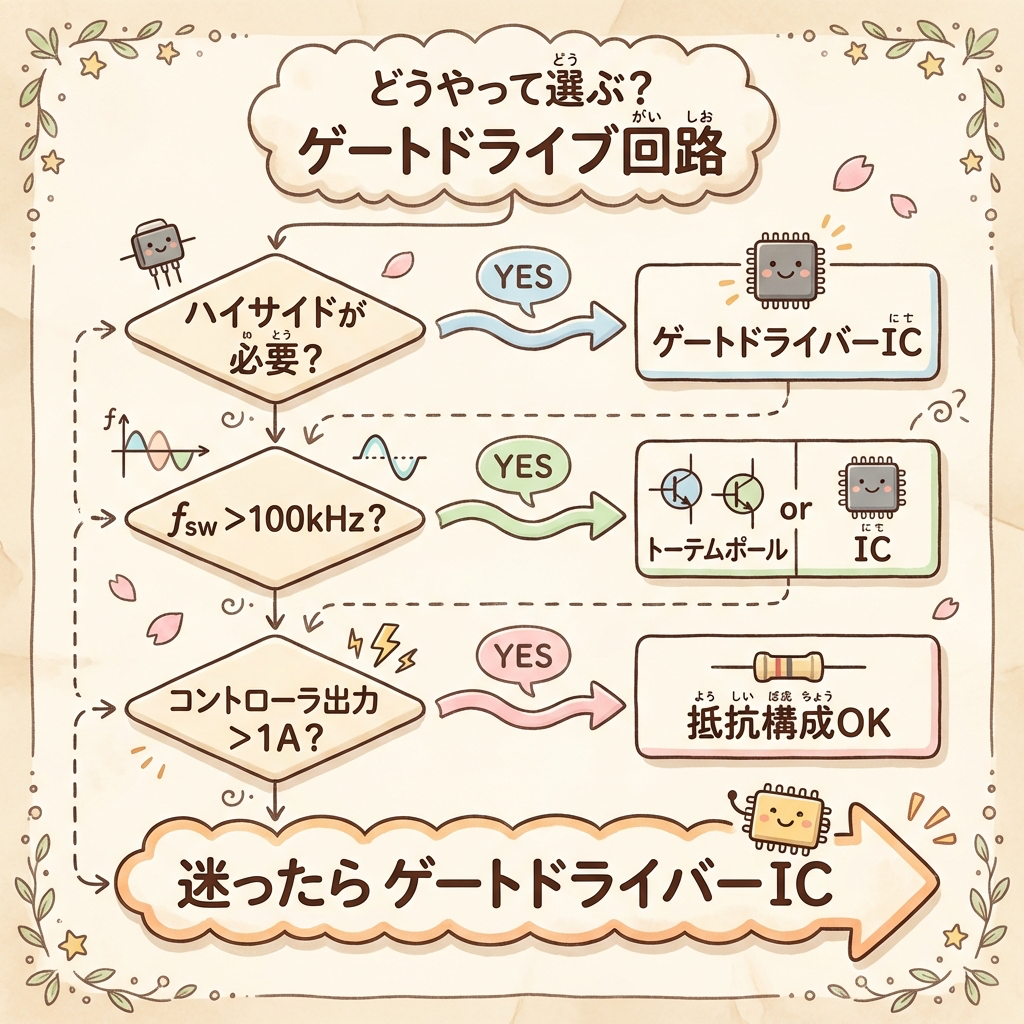

どの構成を選ぶか?──判断フローチャート

5つの構成を紹介しましたが、実際に設計するとき「どれを使えばいいの?」と迷うこともあるでしょう。以下のフローチャートで判断できます。

→ YESの場合:❺ ゲートドライバIC(ハーフブリッジ型 or 絶縁型)一択です。ディスクリートでハイサイドを組むのは上級者でも困難です。

→ YESの場合:❸〜❺のトーテムポール系が必須。抵抗だけの構成ではスイッチング損失が爆発します。

→ コントローラ自体が1〜2Aのソース/シンク能力を持っている場合(TIのUCCシリーズなど):❶❷の抵抗構成でもOKな場合があります。

→ 10〜20mA程度の一般的なコントローラ:❸〜❺で電流を増幅する必要があります。

→ 極限まで部品点数を減らしたい量産品:❸ NPN/PNPトーテムポール(ディスクリート2個で実現可能)

→ それ以外:❺ ゲートドライバICが最も安全・確実です。

設計経験が浅い段階では、「とりあえずゲートドライバIC」で設計を始めるのが正解です。保護機能が内蔵されているため、うっかりミスで素子を壊すリスクが格段に下がります。ディスクリートで組むのは、ICの性能では足りない場合や、回路動作を深く理解したい学習段階で試せば十分です。

実務で気をつけるべき3つのポイント

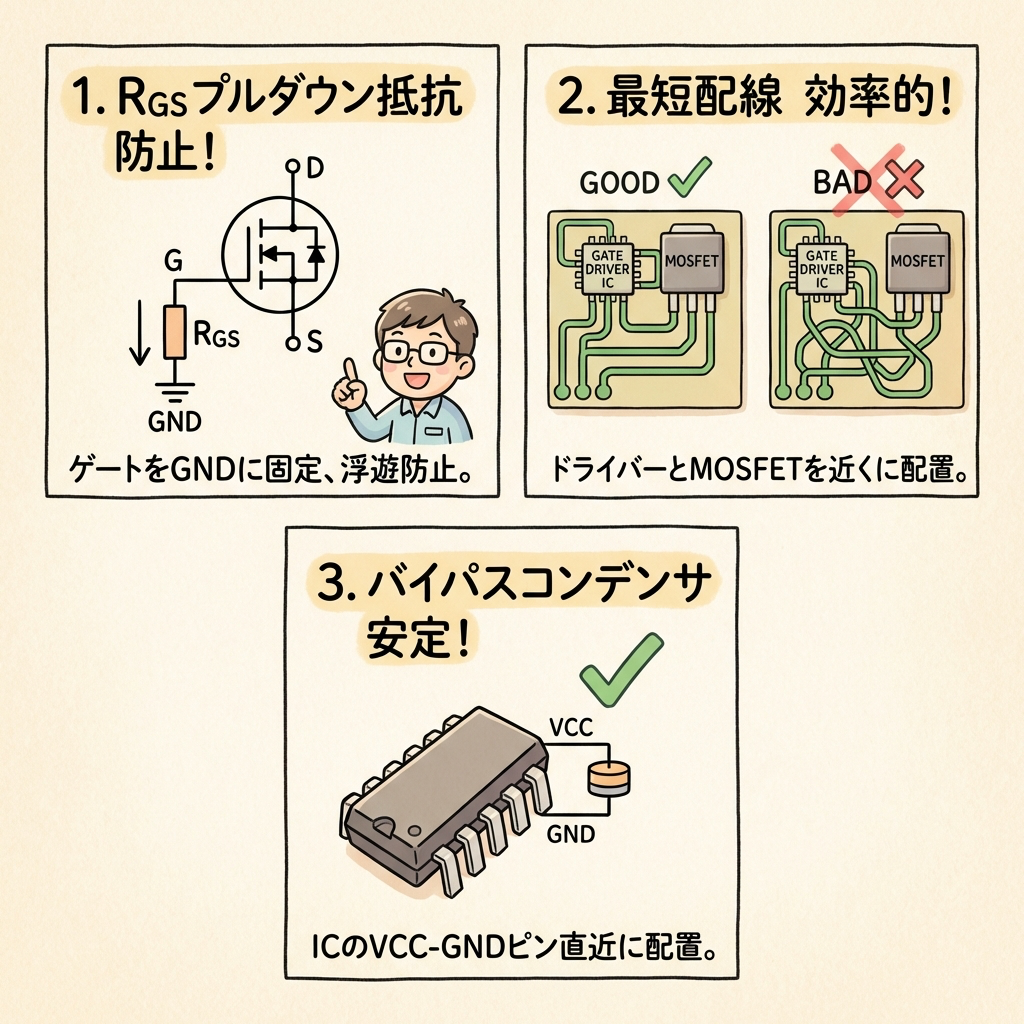

① ゲート-ソース間のプルダウン抵抗(RGS)を忘れない

MOSFETのゲートがどこにも接続されていない「フローティング」状態になると、ノイズによって勝手にONしてしまう危険性があります。特に、システム起動前や駆動回路の電源がまだ立ち上がっていない段階で、MOSFETが意図せずONすると壊滅的な事故になりかねません。これを防ぐために、ゲート-ソース間に10kΩ〜100kΩ程度のプルダウン抵抗を入れるのが鉄則です。

② ゲート配線は「最短・最小ループ」で

ゲート駆動回路からMOSFETのゲートまでの配線が長いと、配線のインダクタンスによりリンギング(発振)が発生します。高周波のリンギングは、MOSFETを高速でON/OFFさせて素子を破壊する原因になります。ゲートドライバICはMOSFETのできるだけ近くに配置し、ゲート-ソース間の配線ループ面積を最小にしてください。

③ バイパスコンデンサは「IC直近」に配置する

ゲートドライバICがゲート容量を充電する瞬間、ICのVCC端子から大きなパルス電流が流れます。この電流を安定供給するために、ICのVCC-GND間にセラミックコンデンサ(0.1μF〜1μF)をできるだけ短い配線で接続してください。これが離れていると、電源電圧が瞬間的にドロップしてICが誤動作する原因になります。

まとめ:ゲート駆動回路は「MOSFETを生かすも殺すもする裏方」

② なぜ必要か:ゲートは「コンデンサ」だから。電圧だけでなく「電流」が必要

③ マイコン直結がダメな理由:電圧不足(3.3V vs 12V)、電流不足(10mA vs 1A)、ハイサイド駆動不可

④ 回路構成は5段階:抵抗1本 → ON/OFF個別抵抗 → NPN/PNPトーテムポール → PMOS/NMOSトーテムポール → ゲートドライバIC

⑤ 実務ではゲートドライバICが標準:保護機能込みで安全・確実

パワーエレクトロニクスの回路設計では、MOSFETやIGBTの選定に時間をかける一方で、ゲート駆動回路を「とりあえず」で済ませてしまうケースがあります。しかし、スイッチング損失、EMI、素子の信頼性──これらすべてにゲート駆動回路の品質が直結しています。

この記事で「なぜゲート駆動回路が必要なのか」という本質を理解できたら、次はより深いトピック──ブートストラップ回路の詳細設計、ゲート抵抗の計算方法、ゲートドライブ配線のパターン設計──に進んでみてください。

📚 次に読むべき記事

ゲートドライバICの内部構造、ハイサイド/ローサイドの仕組みをさらに深掘りする記事

ハイサイドMOSFETをどうやって駆動するのか、ブートストラップ回路の動作原理を完全解説

ゲート抵抗RGの値をどう決めるか、具体的な計算例とトレードオフの考え方

パワーエレクトロニクスの知識は、電験三種の「機械」科目でも問われます。もし「資格を取ることで自分の市場価値を上げたい」と感じているなら、こちらの記事も参考にしてみてください。

「電験三種で人生変わる」は本当か?30代で取得した私の体験談 →