- 短絡保護(SCP)って過電流保護(OCP)と何が違うの?

- デサチュレーション検出の仕組みがよくわからない

- なぜ短絡時に「ゆっくり」OFFしないといけないの?

- ブランキング時間の設定方法がわからない

- 短絡保護(SCP)と過電流保護(OCP)の違い

- デサチュレーション検出の原理と回路構成

- ソフトシャットダウンが必要な理由と実装方法

- ブランキング時間・閾値電圧の設計指針

パワーエレクトロニクス回路において、短絡事故は最も破壊的なトラブルの一つです。短絡が発生すると、MOSFETやIGBTには定格の10倍以上の電流が一瞬で流れ、数マイクロ秒で素子が破壊されてしまいます。

「過電流保護(OCP)があれば大丈夫でしょ?」と思うかもしれません。しかし、OCPでは短絡を防げないのです。なぜなら、OCPは「じわじわ増える過負荷」を検出する仕組みであり、「一瞬で爆発的に増える短絡電流」には間に合わないから。

この記事では、短絡からスイッチング素子を守る「短絡保護(SCP:Short Circuit Protection)」の設計方法を、図解でわかりやすく解説します。

目次

短絡保護(SCP)とは?過電流保護(OCP)との違い

まず、短絡保護と過電流保護の違いを明確にしましょう。この2つは「守る対象」も「検出速度」もまったく異なります。

過電流保護(OCP):「じわじわ系」の番人

過電流保護(OCP)は、負荷が重すぎて定格を超える電流が流れ続ける状態を検出します。たとえば、モーターが過負荷で回転数が落ち、電流が徐々に増加するようなケースです。

OCPの特徴は以下の通りです:

- 検出方法:シャント抵抗やCT(カレントトランス)で電流を測定

- 応答速度:数十μs〜数百μs(比較的ゆっくり)

- 保護対象:負荷側の機器、配線の過熱防止

- 動作後:即座にOFFしても問題ない

短絡保護(SCP):「一瞬で爆発系」の最後の砦

短絡保護(SCP)は、出力端子が短絡して爆発的に電流が増加する状態を検出します。短絡電流は1μs以内に定格の10倍以上に達することもあり、OCPでは絶対に間に合いません。

SCPの特徴は以下の通りです:

- 検出方法:デサチュレーション検出(VCE/VDS監視)

- 応答速度:数百ns〜数μs(超高速)

- 保護対象:スイッチング素子(MOSFET/IGBT)そのもの

- 動作後:ソフトシャットダウン必須(急にOFFすると壊れる)

OCPとSCPの比較表

| 項目 | 過電流保護(OCP) | 短絡保護(SCP) |

|---|---|---|

| 検出対象 | 過負荷電流(定格の1.2〜2倍) | 短絡電流(定格の5〜10倍以上) |

| 検出方法 | シャント抵抗 / CT | デサチュレーション検出 |

| 応答速度 | 数十μs〜数百μs | 数百ns〜数μs |

| 保護対象 | 負荷・配線 | スイッチング素子 |

| OFF方法 | 即時OFF可能 | ソフトシャットダウン必須 |

OCPとSCPはどちらか一方ではなく、両方必要です。OCPは「慢性的な過負荷」、SCPは「急性の短絡」という異なる脅威に対応します。

デサチュレーション検出とは?原理を図解で理解する

短絡保護の核心技術が「デサチュレーション検出(Desaturation Detection)」です。「デサチュ」と略されることも多いこの技術、名前は難しそうですが、原理は意外とシンプルです。

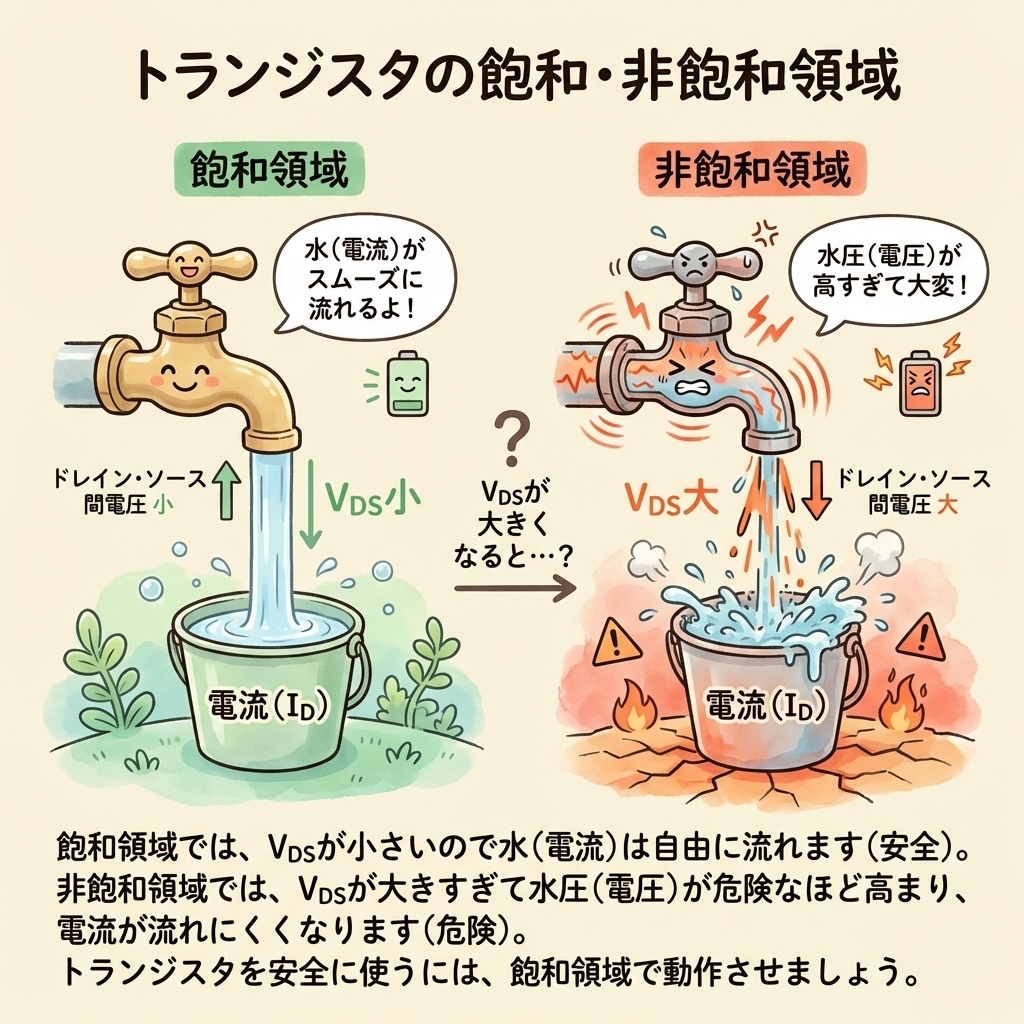

「飽和」と「非飽和」:MOSFETの2つの顔

デサチュレーション検出を理解するには、まずMOSFETやIGBTの「飽和領域」と「非飽和領域」を知る必要があります。

スイッチング素子は、水道の蛇口に例えるとわかりやすいです:

- 飽和領域(ON状態):蛇口を全開にした状態。水(電流)がドバドバ流れ、蛇口での抵抗(VDS/VCE)はほとんどない

- 非飽和領域(短絡状態):配管が詰まって水圧が異常に高くなった状態。蛇口にものすごい圧力(電圧)がかかる

正常動作時、MOSFETは「飽和領域」で動作し、ドレイン-ソース間電圧(VDS)は非常に小さい(数百mV〜数V程度)。しかし短絡が発生すると、電流が爆発的に増加し、MOSFETは「非飽和領域」に追い出され、VDSが急上昇します。

VDS(またはVCE)を監視し、閾値を超えたら「短絡発生」と判断

正常時と短絡時の動作比較

正常動作時(飽和領域)

- 電流:定格内(例:50A)

- VDS:低い(例:1〜2V)

- 素子:全然余裕

- 状態:蛇口全開でスムーズに流れる

短絡発生時(非飽和領域)

- 電流:定格の5〜10倍(例:500A)

- VDS:急上昇(例:7〜10V以上)

- 素子:数μsで破壊の危機

- 状態:配管詰まりで蛇口に異常な圧力

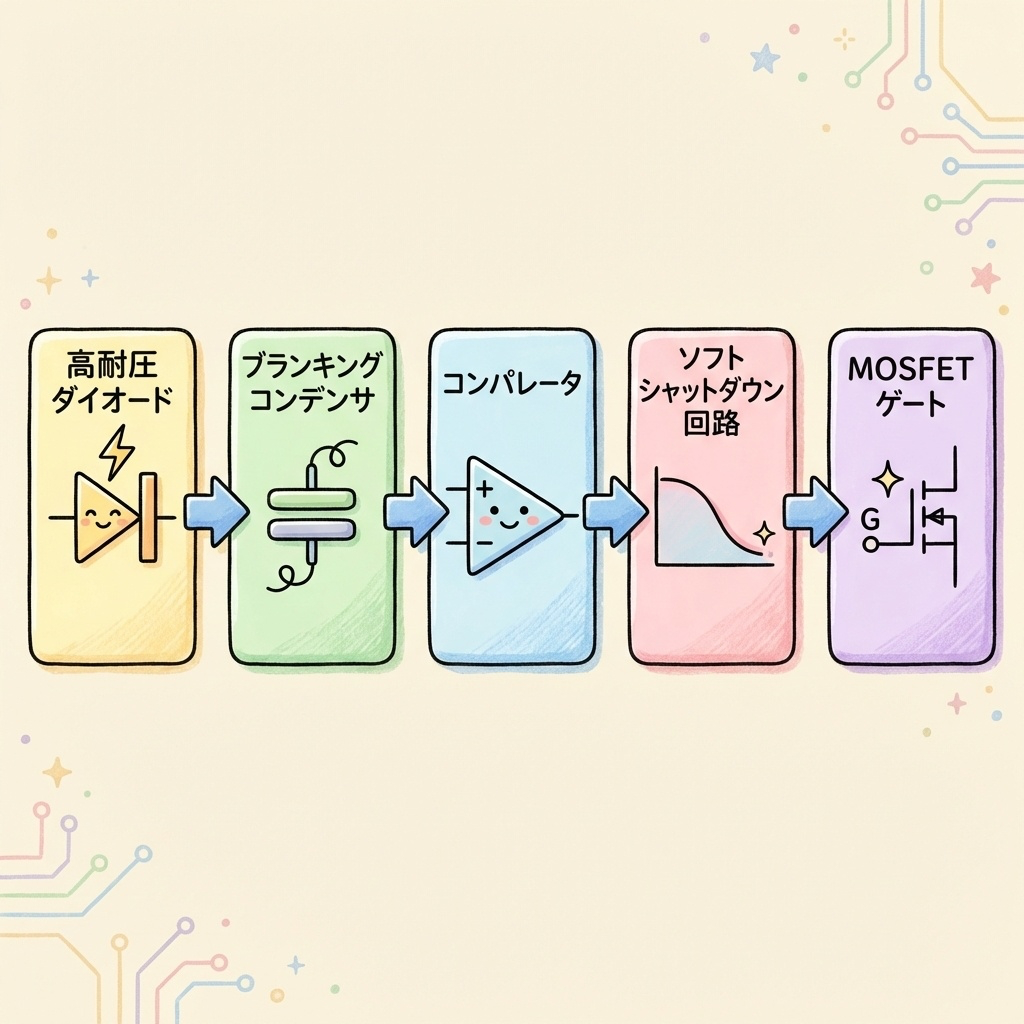

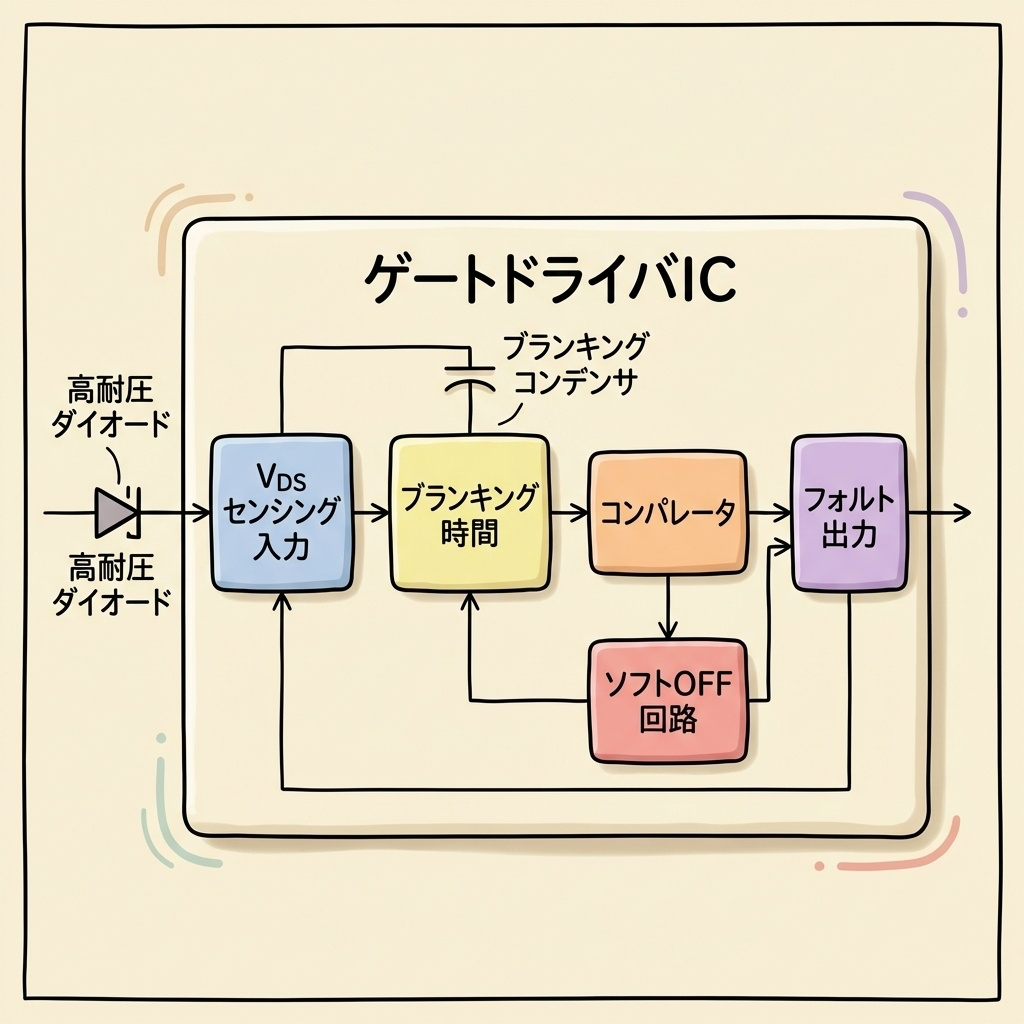

デサチュレーション検出回路の基本構成

デサチュレーション検出回路は、以下の4つの要素で構成されます:

高耐圧ダイオード:MOSFETのドレイン端子から、高電圧がゲートドライバICに直接かからないようにブロック。通常500V〜1200V耐圧のものを使用。

ブランキングコンデンサ:ターンON直後の「正常なVDS上昇」を無視するための時定数を作る。誤検出防止の要。

コンパレータ:VDSと閾値電圧を比較し、閾値を超えたらFAULT信号を出力。ゲートドライバIC内蔵の場合が多い。

ソフトシャットダウン回路:FAULT検出後、ゲート電圧を「ゆっくり」下げて安全にOFFする。急激なOFFはサージ電圧で素子を壊す。

デサチュレーション検出の動作フロー

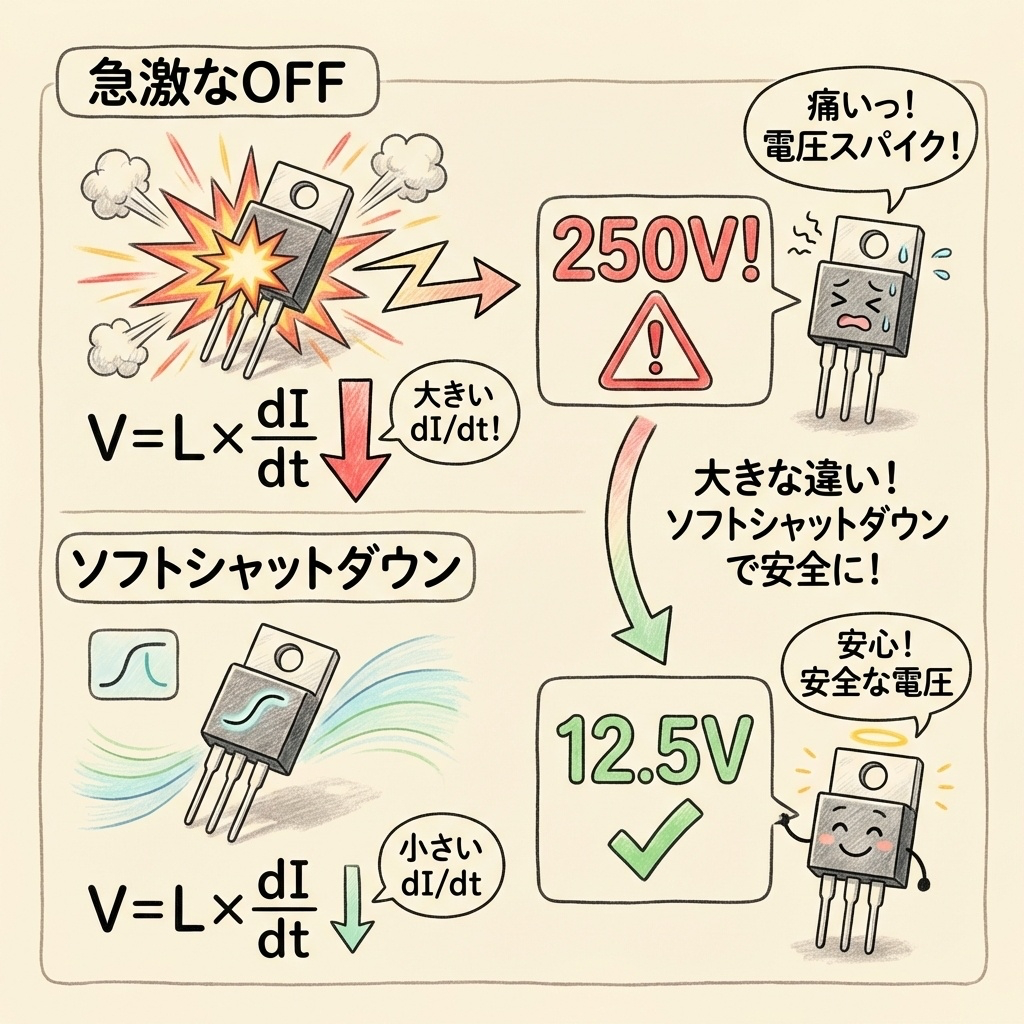

なぜソフトシャットダウンが必要なのか?

短絡を検出したら、すぐにOFFすればいいと思いますよね?しかし、短絡時に「急激に」OFFすると、素子が壊れます。これが短絡保護の最も重要なポイントです。

急激なOFFが危険な理由:L × dI/dt のサージ電圧

短絡時には、定格の5〜10倍もの大電流が流れています。この大電流を一瞬で遮断すると、配線インダクタンスによって巨大なサージ電圧が発生します。

L:配線インダクタンス、dI/dt:電流の変化速度

たとえば、配線インダクタンスが50nH、短絡電流500Aを100nsで遮断した場合:

L = 50nH = 50 × 10-9 H

dI = 500A

dt = 100ns = 100 × 10-9 s

Vsurge = 50 × 10-9 × (500 ÷ 100 × 10-9) = 250V

電源電圧400Vの回路なら、400V + 250V = 650VがMOSFETにかかります。

600V耐圧の素子を使っていたら、一発で破壊です。

ソフトシャットダウン:「ゆっくり」OFFしてサージを抑える

ソフトシャットダウンとは、ゲート電圧を「ゆっくり」下げることで、dI/dtを小さくしてサージ電圧を抑える技術です。

先ほどの例で、遮断時間を100nsから2μsに延ばすと:

dt = 2μs = 2000 × 10-9 s(100nsの20倍)

Vsurge = 50 × 10-9 × (500 ÷ 2000 × 10-9) = 12.5V

サージ電圧が250V → 12.5Vに激減!

電源電圧と合わせても412.5Vとなり、600V素子でも十分余裕があります。

ソフトシャットダウン中も素子には大電流が流れ続けるため、短絡耐量時間(tsc)を超えないよう設計する必要があります。一般的なIGBTのtscは5〜10μs程度です。

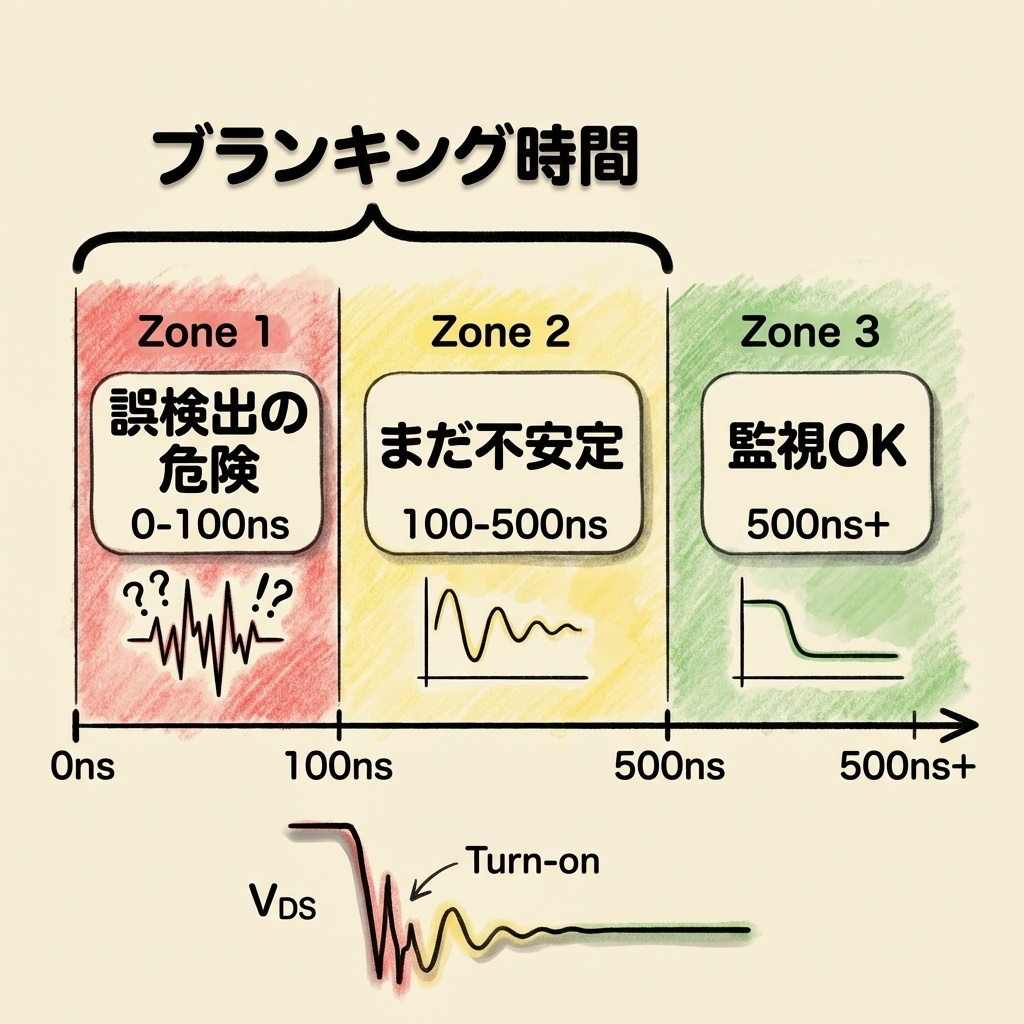

ブランキング時間の設計|誤検出を防ぐ重要パラメータ

デサチュレーション検出で最も難しいのが「ブランキング時間(Blanking Time)」の設定です。これを間違えると、正常動作なのに短絡と誤判定してしまいます。

なぜブランキング時間が必要なのか?

MOSFETやIGBTは、ターンON直後に一時的にVDSが高くなる現象があります。これは正常な動作であり、短絡ではありません。

ターンON時のVDS挙動を時系列で見てみましょう:

| 時間 | 状態 | VDS | 短絡? |

|---|---|---|---|

| 0ns | OFF状態 | 電源電圧(例:400V) | — |

| 0〜100ns | ターンON中 | 急降下中(まだ高い) | 誤検出の危険 |

| 100〜500ns | ON移行中 | 徐々に低下 | まだ不安定 |

| 500ns〜 | 完全ON(飽和) | 安定して低い(1〜2V) | 監視OK |

ブランキング時間とは、ターンON直後の「正常なVDS高い期間」を無視して、誤検出を防ぐための待ち時間です。

ブランキング時間の設計指針

ブランキング時間の設定は、以下の条件を満たす必要があります:

ターンON時間 < ブランキング時間 < 短絡耐量時間(tsc)

| パラメータ | 典型値 | 設定の考え方 |

|---|---|---|

| ターンON時間 | 100ns〜500ns | データシートで確認 |

| ブランキング時間 | 1μs〜3μs | ターンON時間の2〜5倍 |

| 短絡耐量時間(tsc) | 5μs〜10μs | データシートで確認 |

ブランキング時間は「短すぎると誤検出」「長すぎると保護が遅れる」のトレードオフです。最初は2μs程度で設計し、実機で波形を見ながら調整するのが現実的です。

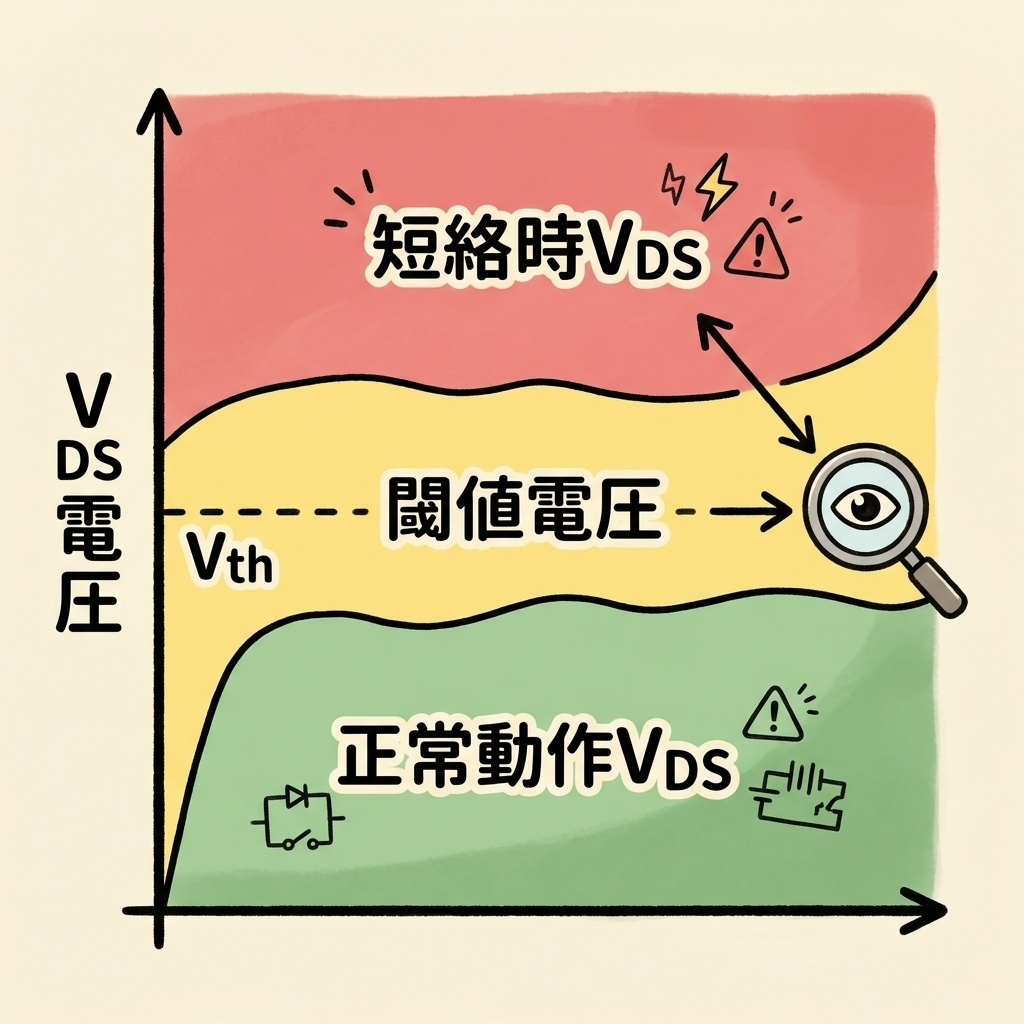

閾値電圧(VDS(th))の設定|どこで「短絡」と判断するか

デサチュレーション検出のもう一つの重要パラメータが「閾値電圧」です。VDSがいくつを超えたら短絡と判断するかを決めます。

閾値電圧の設定指針

閾値電圧は、以下の条件を満たす必要があります:

正常時VDS(max) < 閾値電圧 < 短絡時VDS

| 素子タイプ | 正常時VDS/VCE | 推奨閾値電圧 |

|---|---|---|

| Si MOSFET | 0.5〜2V | 5〜7V |

| IGBT | 1.5〜3V | 7〜9V |

| SiC MOSFET | 1〜3V | 4〜6V |

SiC MOSFETは、Si MOSFETやIGBTに比べて短絡耐量時間が短い(1〜3μs程度)ため、より高速な検出と保護が必要です。閾値電圧も低めに設定し、早期検出を優先します。

ゲートドライバICのデサチュレーション保護機能

実際の設計では、デサチュレーション検出機能を内蔵したゲートドライバICを使うのが一般的です。自分で回路を組むより、ICに任せた方が確実で安全です。

デサチュレーション保護内蔵の代表的なゲートドライバIC

| メーカー | 代表型番 | 特徴 |

|---|---|---|

| Texas Instruments | UCC21750 | SiC/GaN対応、高速DESAT |

| Infineon | 1EDI EiceDRIVER | IGBT向け、ソフトOFF内蔵 |

| Silicon Labs | Si828x | 絶縁型、設定可能なブランキング |

| STMicroelectronics | STDRIVEG600 | GaN対応、高速応答 |

ゲートドライバICを選ぶ際は、以下を確認しましょう:

① デサチュレーション検出機能の有無

② ブランキング時間の設定範囲(外付け部品で調整可能か)

③ ソフトシャットダウン機能の有無と方式

④ FAULT出力の仕様(ラッチ/非ラッチ)

短絡保護(SCP)の設計チェックリスト

最後に、短絡保護を設計する際のチェックリストをまとめます。これを確認しながら設計を進めれば、漏れなく保護回路を構築できます。

設計チェックリスト

| ✓ | 確認項目 | ポイント |

|---|---|---|

| □ | スイッチング素子の短絡耐量時間(tsc) | データシートで確認(5〜10μs程度) |

| □ | ブランキング時間の設定 | ターンON時間の2〜5倍、tsc未満 |

| □ | 閾値電圧の設定 | 正常時VDS(max)より十分高く設定 |

| □ | ソフトシャットダウン時間 | サージ電圧が耐圧を超えないか確認 |

| □ | 高耐圧ダイオードの選定 | 電源電圧以上の耐圧、低VF品を選択 |

| □ | FAULT信号の処理 | マイコンへの通知、システム停止処理 |

| □ | 実機での波形確認 | 短絡模擬テストで動作検証 |

まとめ|短絡保護は「最後の砦」

この記事では、短絡保護(SCP)の設計方法を解説しました。重要なポイントをおさらいしましょう。

- 短絡保護(SCP)と過電流保護(OCP)は別物:OCPは「じわじわ系」、SCPは「一瞬で爆発系」に対応

- デサチュレーション検出:VDS/VCEの上昇を監視して短絡を高速検出

- ソフトシャットダウン必須:急激なOFFはL×dI/dtのサージで素子を壊す

- ブランキング時間:ターンON時間<ブランキング時間<短絡耐量時間

- ゲートドライバIC活用:デサチュレーション検出内蔵ICを使うのが確実

短絡保護は、パワーエレクトロニクス回路の「最後の砦」です。この保護がしっかり機能すれば、万が一の短絡事故でも高価なスイッチング素子を守ることができます。

設計の際は、必ず実機で短絡模擬テストを行い、保護が正しく動作することを確認してください。

📚 次に読むべき記事

短絡保護と組み合わせて使う過電流保護の設計方法を解説。検出素子の選び方から回路構成まで。

デサチュレーション保護を内蔵したゲートドライバICの選び方と使い方を解説。

短絡保護と併用するスナバ回路の設計。サージ電圧対策の基本を学ぶ。

高効率な回路を設計することも重要ですが、「壊れない」設計はそれ以上に重要です。保護回路をしっかり設計して、安心・安全な製品を作りましょう。