回路設計の佐藤先輩から「このDC-DCコンバータ、効率もう少し上げたいんだよね。スイッチング速度上げてみて」と振られた田中さん。「速度を上げる」って具体的に何をどうすれば?ゲート抵抗を小さくすればいい?それで本当に効率が上がる?

調べてみると「dV/dt」「dI/dt」「ターンオン時間」「ターンオフ時間」「スイッチング損失」と専門用語が次々出てくる。しかも「速くするとEMIノイズが悪化する」「速すぎるとデバイスが壊れる」とも書いてある。結局、速くすればいいのか、しないほうがいいのか、どっちなんだ?

結論を先に言います。スイッチング速度には「最適点」があり、速ければ速いほど良いわけではありません。本記事で、速度を決める3つの要素と、速度を上げすぎると何が壊れるのかを完全図解します。

- 「dV/dt」「dI/dt」が何のことか実はよくわかっていない

- ゲート抵抗を変えると何が起きるのか説明できない

- スイッチング速度を上げたのにEMI試験で落ちた

- 「速ければ効率が上がる」と思っていたら逆に発熱が増えた

- スイッチング速度を決める3つの要素を1枚絵で理解

- dV/dtとdI/dtの違いと、それぞれが引き起こすトラブル

- 「速くする」と「遅くする」のトレードオフを5つの視点で整理

- 実際に速度をチューニングする実務手順

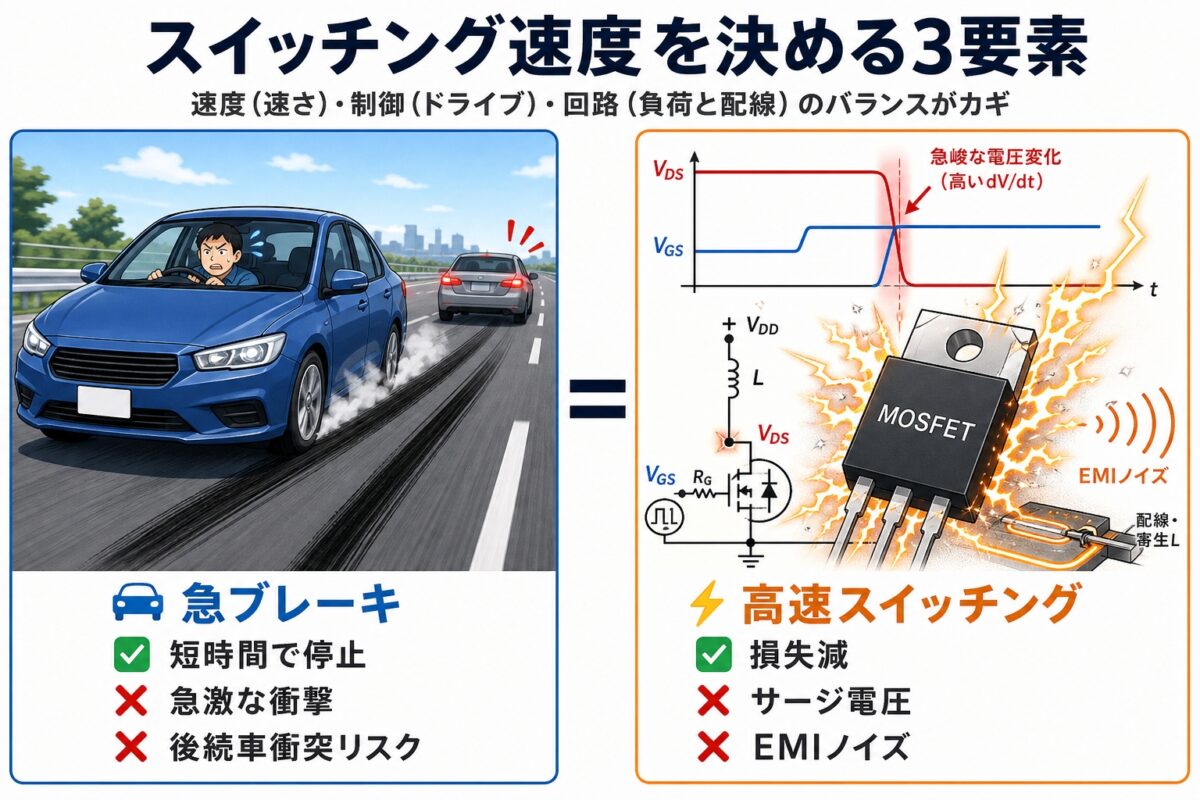

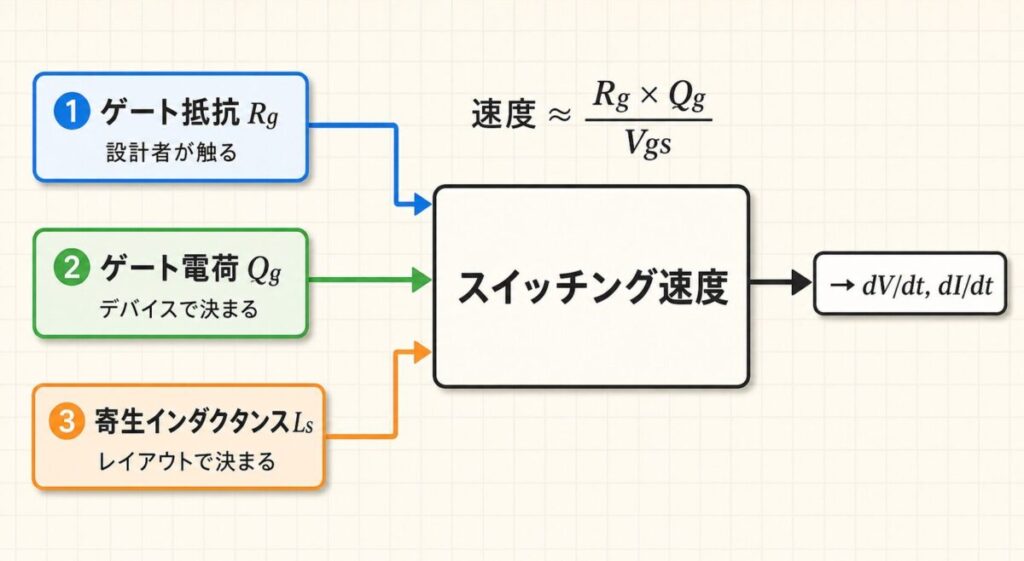

スイッチング速度は「ゲート抵抗」「ゲート電荷Qg」「寄生インダクタンス」の3つで決まります。速くするとスイッチング損失は減るけど、EMIノイズ・サージ電圧・誤動作リスクが増える。「車の急ブレーキ」と同じで、速い操作には必ずリスクが伴います。

目次

そもそも「スイッチング速度」とは?「車のブレーキ」と同じ

スイッチング速度とは、MOSFETやIGBTがONからOFF(またはOFFからON)に切り替わるまでの時間のこと。単位はナノ秒(ns)〜マイクロ秒(μs)のオーダーです。

わかりにくいので「車のブレーキ」で例えます。時速60kmで走っている車を停止させるとき、踏み方で大きく違いますよね。

急ブレーキ(速いスイッチング)

- 停止までの時間: 短い ✅

- ブレーキ消耗: 少ない ✅

- 急停止のショック: 大 ❌

- 後続車に追突されるリスク: 大 ❌

緩やかなブレーキ(遅いスイッチング)

- 停止までの時間: 長い ❌

- ブレーキ消耗: 多い ❌

- 急停止のショック: 小 ✅

- 後続車に追突されるリスク: 小 ✅

スイッチング速度もまったく同じです。速ければ「切り替え時間が短く損失が減る」というメリットがあるけど、「サージ電圧やEMIノイズが暴れる」というデメリットも同時に発生します。

スイッチング速度を表す2つの指標

| 指標 | 意味 | 単位 |

|---|---|---|

| dV/dt | 電圧の変化の速さ (1秒あたり何V変化したか) |

V/ns V/μs |

| dI/dt | 電流の変化の速さ (1秒あたり何A変化したか) |

A/ns A/μs |

dV/dtは「電圧がどれだけ急峻に立ち上がる/立ち下がるか」。dI/dtは「電流がどれだけ急峻に変化するか」。この2つを区別できるかが、パワエレ設計のスタートラインです。両者は別物で、引き起こすトラブルも別。

スイッチング速度を決める3つの要素

本題です。スイッチング速度は基本的に3つの要素で決まります。これを理解すれば、「どこをいじれば速度が変わるか」が見えるようになります。

ゲート抵抗 Rg

ゲートに接続される抵抗値。ゲート容量を充電/放電するスピードを決める。設計者が一番触りやすいパラメータ。Rgを小さくすればスイッチングは速くなる。

ゲート電荷 Qg

MOSFETのゲートを充電するのに必要な電荷量(単位: nC)。デバイスの選定で決まる。Qgが小さいデバイスほど高速スイッチングが可能。データシートのキー指標。

寄生インダクタンス Ls

ドレイン-ソース経路、ゲート配線、PCBレイアウトに含まれる「見えないコイル」。速いdI/dtと組み合わさってサージ電圧を発生させる元凶。基板設計で最小化する。

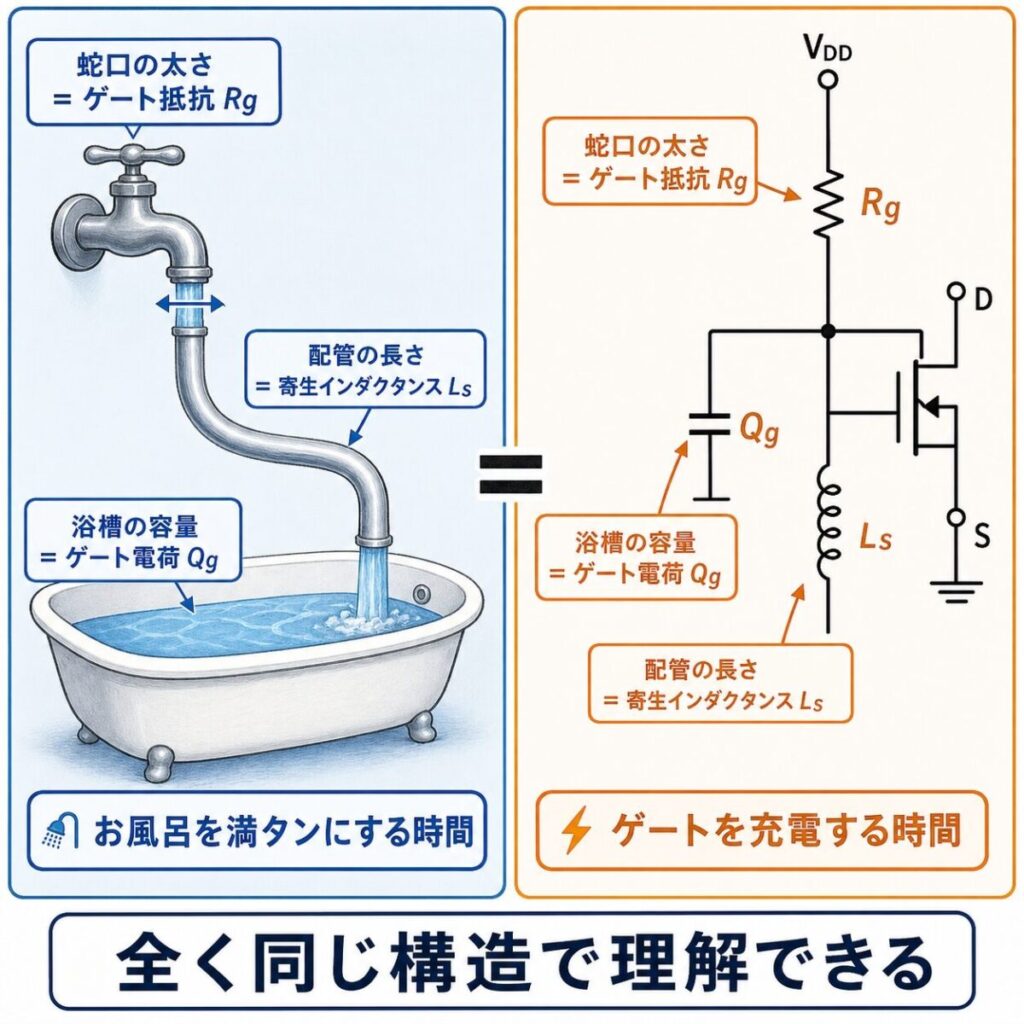

3つの要素を「水道蛇口」で理解する

3つの要素の関係を「お風呂を蛇口で満タンにする時間」で例えると一発でわかります。

| 電気の世界 | 水道の世界 | 速度への影響 |

|---|---|---|

| ゲート抵抗 Rg | 蛇口の太さ | 細いと水流が遅い→充電遅い |

| ゲート電荷 Qg | 浴槽の容量 | 大きいとお湯張りに時間かかる |

| 寄生インダクタンス Ls | 配管の長さと曲がり | 急に止めるとウォーターハンマー(サージ) |

スイッチング時間 ≈ Rg × Qg / Vgs

ゲート抵抗が大きいほど、ゲート電荷が大きいほど、スイッチング時間は長くなります(=遅くなる)。Vgsはゲート駆動電圧。

ゲート抵抗の決め方|Qgから抵抗値を計算する設計手順 →

要素①ゲート抵抗 Rg|設計者が一番触る「速度ダイヤル」

ゲート抵抗 Rg は、設計者が後から自由に変えられる唯一の要素です。同じMOSFETを使っていても、Rgを変えるだけでスイッチング速度はガラッと変わります。

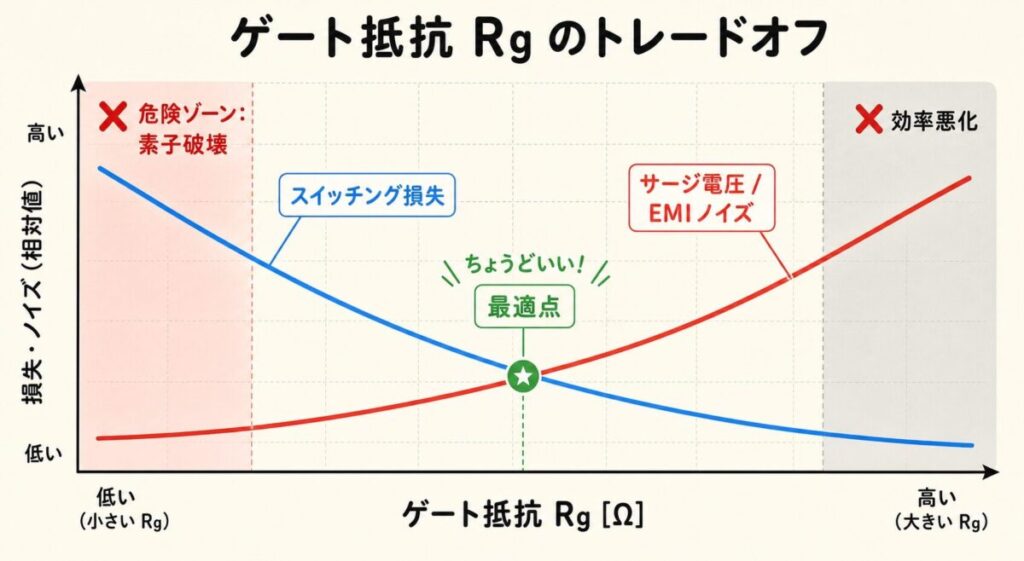

Rgを変えると何が変わるか?

| 項目 | Rg小(速い) | Rg大(遅い) |

|---|---|---|

| スイッチング時間 | 短い ✅ | 長い ❌ |

| スイッチング損失 | 小 ✅ | 大 ❌ |

| dV/dt・dI/dt | 大 ❌ | 小 ✅ |

| サージ電圧 | 大 ❌ | 小 ✅ |

| EMIノイズ | 大 ❌ | 小 ✅ |

| リンギング | 大 ❌ | 小 ✅ |

Rgを下げて損失を減らそうとすると、サージ・EMIノイズ・リンギングが悪化します。逆にRgを上げてノイズを抑えようとすると損失が増えて発熱が悪化します。「ちょうどいい中間点」を見つけるのが設計者の腕です。

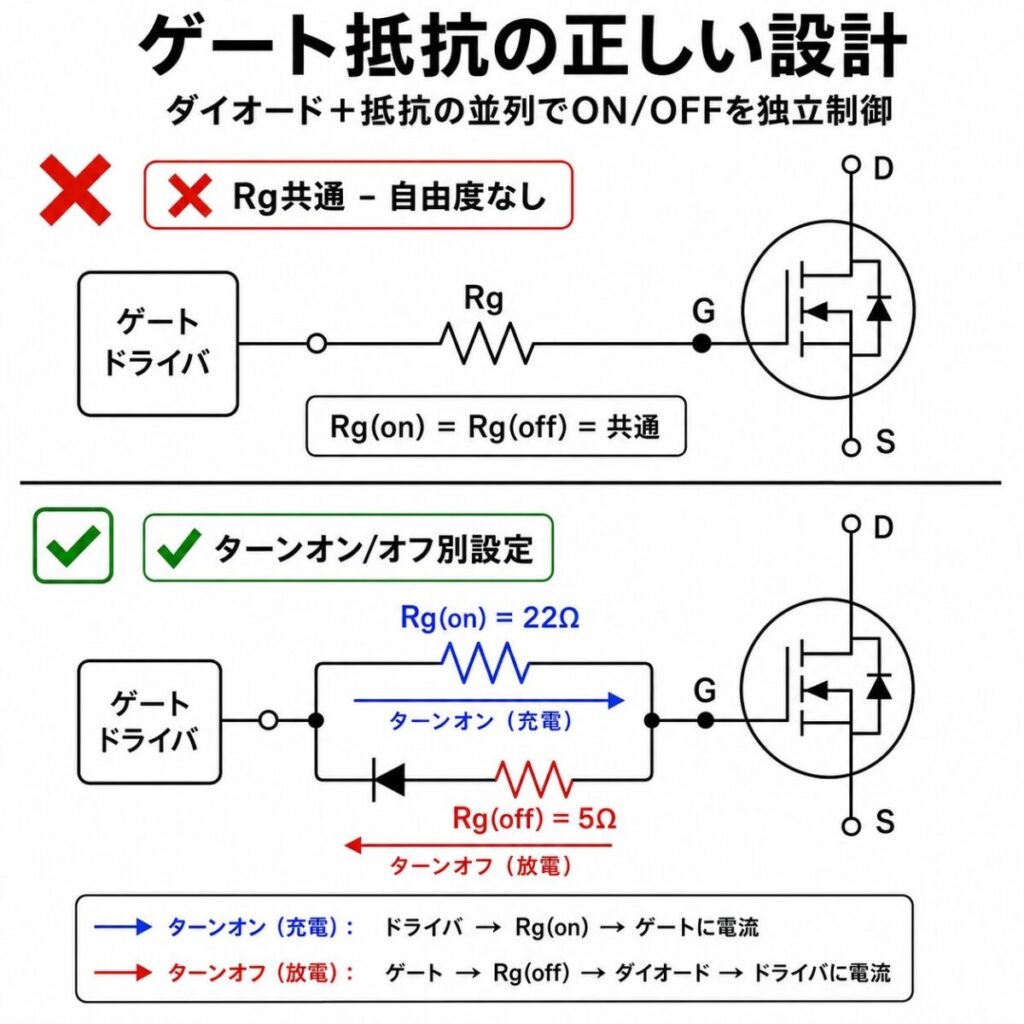

ターンオン用とターンオフ用でRgを分ける

実務では、ターンオンとターンオフでゲート抵抗を別々に設定するのが定石です。なぜなら、それぞれで重視するポイントが違うから。

ターンオン Rg(on)

少し大きめに設定。

急峻なdI/dtを抑え、対向ダイオードのリカバリ電流による誤動作を防ぐ。

目安: 10〜47Ω

ターンオフ Rg(off)

小さめに設定。

素早くゲート電荷を引き抜き、ミラー効果による自己ターンオン誤動作を防ぐ。

目安: 2〜10Ω

ターンオン用とオフ用を分ける典型回路は、ダイオード+抵抗の並列構成。順方向(オン時)はダイオード経由でRg(on)を通し、逆方向(オフ時)はダイオードがオフになりRg(off)経由で放電させる。シンプルで効果的な設計テクです。

要素②ゲート電荷 Qg|デバイス選定で決まる「容量」

ゲート電荷 Qg(単位: nC)は、MOSFETのゲートを完全にONにするために必要な電荷量のこと。データシートに必ず記載されています。Qgが小さいデバイスほど、高速スイッチングが可能です。

Qgには3種類ある

| 記号 | 名称 | 意味 |

|---|---|---|

| Qgs | ゲート-ソース電荷 | ターンオンの初期段階(しきい値到達まで) |

| Qgd | ゲート-ドレイン電荷 (ミラー電荷) |

ミラー期間。最も時間がかかる |

| Qg(total) | 合計ゲート電荷 | 完全ON状態にするまでの総電荷量 |

スイッチング波形を見ると、ゲート電圧が一定値で「踊り場」を作る瞬間があります。これがミラープラトー。Qgdに対応する期間で、ここでスイッチング損失の大半が発生する。低Qgdのデバイスを選ぶと劇的に効率が上がります。

Qgが小さいデバイスを選ぶときの注意点

「じゃあQgが小さいMOSFETを選べばいいんだな!」と思いがちですが、Qgが小さいデバイスにはトレードオフがあります。

| 特性 | Qg小 | Qg大 |

|---|---|---|

| スイッチング速度 | 高速 ✅ | 低速 ❌ |

| オン抵抗 Rds(on) | 大きい傾向 ❌ | 小さい傾向 ✅ |

| 導通損失 | 大 ❌ | 小 ✅ |

| 価格 | 高い傾向 ❌ | 安い ✅ |

MOSFETの総合性能を判断する指標としてFOM = Rds(on) × Qgがよく使われます。FOMが小さいほど「高速かつ低損失」のバランスが良いデバイス。データシート比較時はこの値で評価しましょう。

SiC MOSFETやGaN HEMTがパワエレ業界で注目されている理由は、従来Si MOSFETより圧倒的にQgが小さいから。同じスイッチング速度なら、SiC/GaNを使うとスイッチング損失が1/3〜1/10になります。ただし価格はまだ高い。

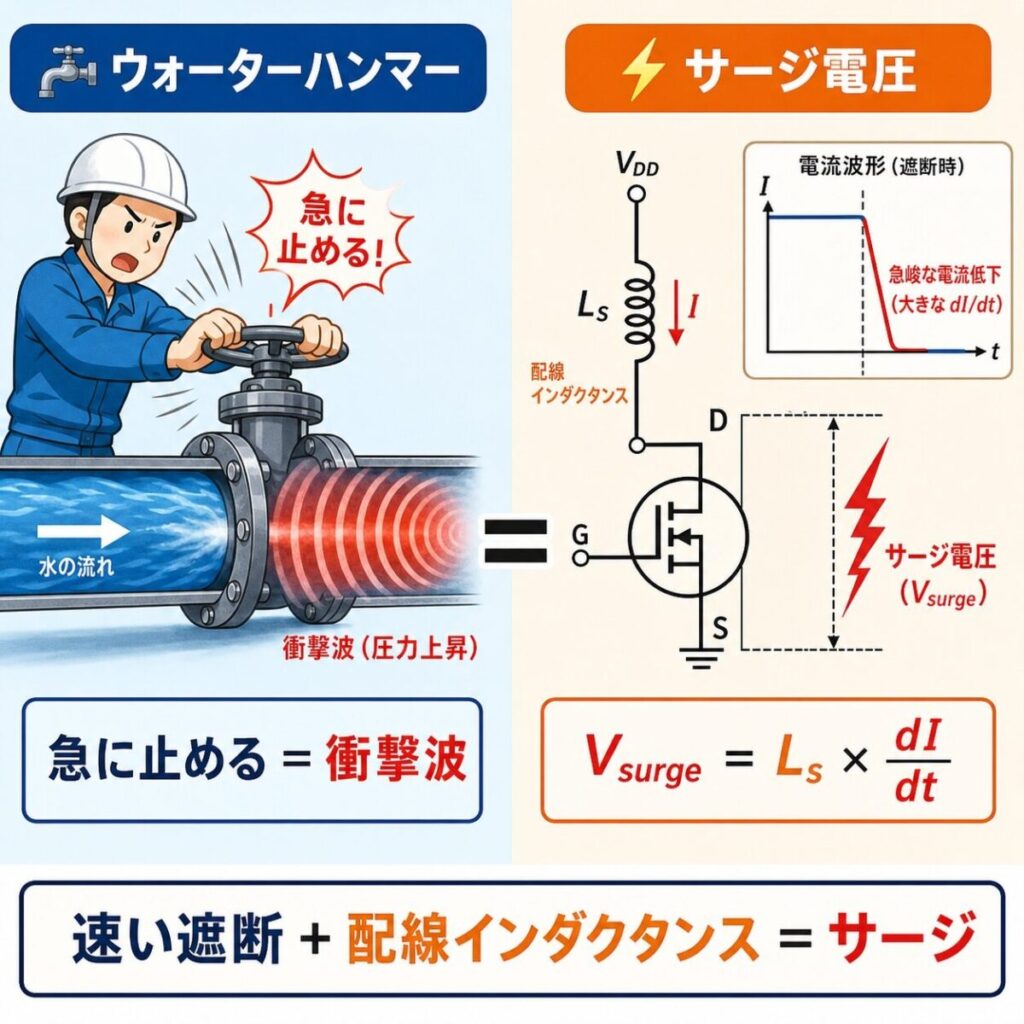

要素③寄生インダクタンス Ls|「見えないコイル」がサージを作る

寄生インダクタンス Ls とは、配線・パッケージ・基板パターンの中に「気づかないうちに」存在する小さなコイル成分のこと。回路図には描かれませんが、確実に存在しています。

なぜこれが重要なのか?速いdI/dtと組み合わさると、サージ電圧を発生させる元凶になるからです。

V_surge = Ls × dI/dt

配線インダクタンス10nH、ターンオフ時のdI/dt=1000A/μsの場合

V_surge = 10×10⁻⁹ × 1×10⁹ = 10Vのサージが発生します。

数値だけ見ると「10V?大したことない」と思うかもしれませんが、これが400V系の電源だと耐圧オーバーで一発でMOSFETが壊れるレベル。実機ではdI/dtがもっと大きく、サージ100V〜数百Vに達することもあります。

寄生インダクタンスがある場所

| 場所 | 典型値 | 対策 |

|---|---|---|

| ドレイン-ソース パワー配線 |

10〜100nH | 配線を太く・短く・帰路を密に |

| パッケージリード | 3〜15nH | SMDパッケージ・ベアダイ採用 |

| ゲート配線 | 5〜30nH | ドライバを近くに、配線を短く |

| 入力コンデンサ配線 | 5〜20nH | FETの真横に配置 |

「Rgを下げてdI/dtを上げる」=「サージが増える」=「Lsを下げないと壊れる」。つまり高速化したいなら、まず基板レイアウトで寄生インダクタンスを減らすのが先です。デバイス選定や定数調整より、レイアウトが先決。

「速くする」メリットとデメリット|5つの視点で整理

ここまでで、スイッチング速度を決める3つの要素がわかりました。じゃあ実際に「速くするか、遅くするか」を判断する基準は?5つの視点で整理します。

視点①スイッチング損失(発熱)

速くすればスイッチング損失は減る。電圧と電流が同時に存在する「重なり期間」が短くなるから。発熱が減って効率が上がるのが最大のメリットです。

P_sw = (1/2) × V × I × (t_on + t_off) × f_sw

スイッチング時間(t_on, t_off)に比例。速くすればそのまま損失が減ります。

視点②サージ電圧(デバイス耐圧)

速くするとサージ電圧が増える。寄生インダクタンスとdI/dtの掛け算で発生するから。耐圧が足りないとMOSFET/IGBTが破壊されます。

視点③EMIノイズ

速くすると放射ノイズ・伝導ノイズが悪化。dV/dtが大きいほど高周波成分が増え、EMI試験で落ちる原因になります。最近のSiC/GaN高速化で最も問題になる視点です。

視点④誤動作リスク(自己ターンオン)

速いdV/dtは、ハイサイド・ローサイドの「もう片方」を意図せずONにする(自己ターンオン現象)。最悪の場合、上下短絡で素子が即破壊。これがハーフブリッジ回路で最も恐れられる現象です。

視点⑤フィルタサイズ(回路全体)

スイッチング周波数を上げるとインダクタとコンデンサが小さくできて回路が小型化。ただし上げすぎるとEMI対策フィルタが大型化して、結局トータルでは大きくなることも。

5視点を一覧で比較

| 視点 | 速くすると | 遅くすると |

|---|---|---|

| スイッチング損失 | 減る ✅ | 増える ❌ |

| サージ電圧 | 増える ❌ | 減る ✅ |

| EMIノイズ | 悪化 ❌ | 改善 ✅ |

| 誤動作リスク | 増える ❌ | 減る ✅ |

| 回路小型化(部品サイズ) | 小型化 ✅ | 大型化 ❌ |

速くするメリットは「損失減」と「小型化」のみ。デメリットは「サージ・EMI・誤動作」の3つ。2勝3敗です。だからこそ、闇雲に速くするのではなく、「許容できる範囲で最大限に速く」するのが正解です。

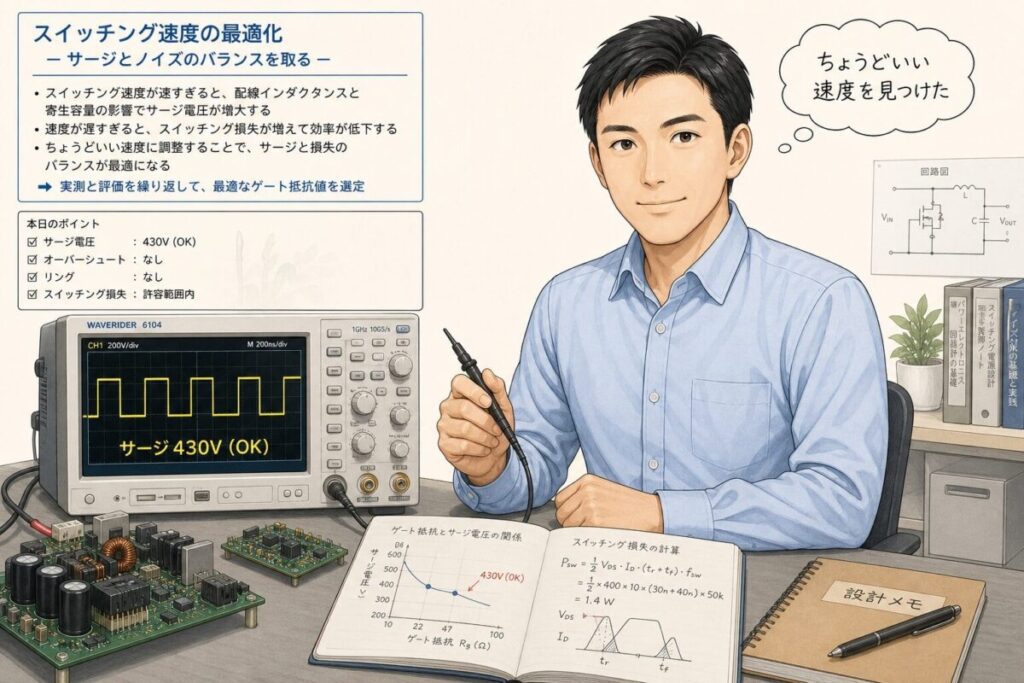

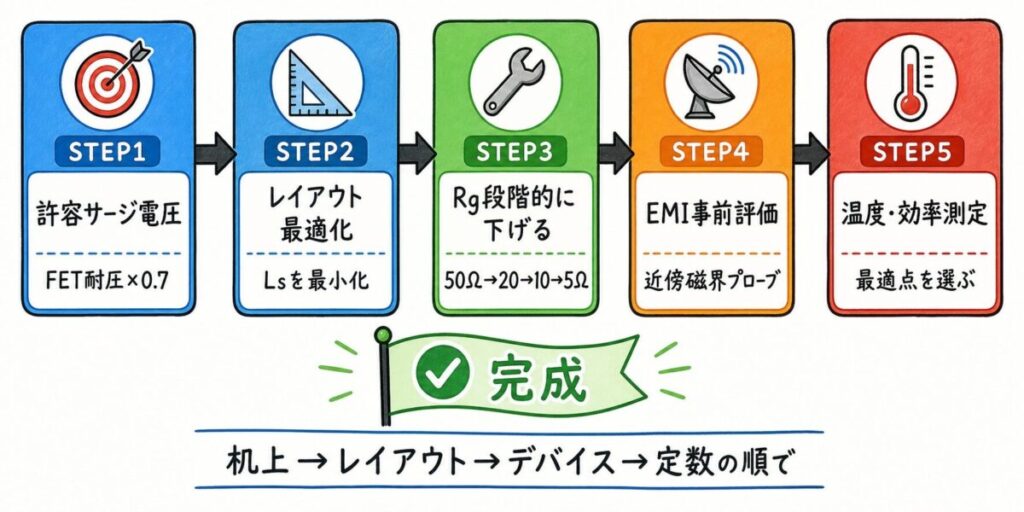

実機でスイッチング速度を最適化する5ステップ

実際にスイッチング速度をチューニングするときの手順を5ステップで紹介します。「とにかくRgを変えて試す」のではなく、論理的に絞り込むのがコツ。

許容サージ電圧を決める

まず「サージ電圧の上限値」を決める。MOSFETの絶対最大定格Vds(max)に対し、ディレーティングで70〜80%が目安。例:600V耐圧FETなら480V以下に抑える。これが速度の物理的な天井になります。

基板レイアウトで寄生インダクタンスを最小化

ドレイン-ソース経路の電流ループ面積を最小化。入力コンデンサをFETの真横に配置。これでLsが半分以下になることも。デバイス選定よりレイアウトが先です。

大きめのRgから始めて段階的に下げる

最初は「安全側」のRgで動作確認。例:50Ωから始めて、20Ω→10Ω→5Ωと段階的に下げ、サージ電圧をオシロで実測する。許容サージを超えた時点で、その1つ前のRgが上限。

EMI事前評価で問題を早期検出

動作確認後、近傍磁界プローブでEMI事前評価。dV/dtが速すぎると100MHz以上の放射ノイズが急増。EMI試験本番で落ちる前に、ここで気づくのが重要です。

温度・効率測定で最終確認

Rgを変えた条件ごとに、FET温度・回路効率・出力リップルを実測してデータ化。「Rg=10Ω時:効率94.5%、FET温度65℃、サージ430V」のような表を作って最適点を選ぶ。

スイッチング速度の最適化は「パワエレ設計者の経験差が一番出る」領域です。データシート通りに作っても動かないことが多く、実機での測定とチューニングが必須。先輩エンジニアに「最初のRgはいくつから始める?」と聞くと、その人の経験値がわかります。

初心者がやりがちなNGパターン4選

NG①「とにかくRgを下げまくる」

「速ければ効率が上がる」と思って、Rgを1Ω以下にする初心者が多い。結果、サージで素子破壊・EMIで認証落ちのコンボを食らう。Rg下げる前に基板レイアウトを見直すのが先です。

NG②データシートのQgだけ見て選定

Qgが小さいデバイスだけを選んでも、Rds(on)が大きいと導通損失が増えます。FOM = Rds(on) × Qgで総合判断するのが正解。トータルロスで比較しましょう。

NG③ターンオン用とターンオフ用のRgを共通にする

Rg(on)とRg(off)を1つの抵抗で兼用すると、最適化の自由度が半減。ダイオード+抵抗の並列構成で別々に設定することで、ターンオンとオフを独立にチューニングできます。コスト増は数円。

NG④寄生インダクタンスを甘く見る

「配線数mmだから誤差程度でしょ」と思ったら大間違い。10mmの配線で約10nH。dI/dt=1A/nsなら10Vのサージが発生する。基板レイアウトでLsを抑えるのは、回路定数調整より優先度高いです。

こうすると失敗

- Rgを1Ω以下に下げる

- Qgだけ見てデバイス選定

- ターンオン/オフのRg共通化

- 寄生インダクタンスを軽視

こうすればOK

- サージ実測しながらRg段階下げ

- FOMでトータル評価

- ダイオード+抵抗で別々設定

- レイアウト最適化を最優先

スイッチング速度のチューニングは「机上→レイアウト→デバイス→定数」の順で進めるのが鉄則。後ろの工程で前の工程の問題は解決できません。レイアウトが悪いまま定数調整しても、いたちごっこで終わります。

まとめ|スイッチング速度には「ちょうどいい」がある

- スイッチング速度はdV/dt(電圧変化率)とdI/dt(電流変化率)で表現

- 速度を決める3要素 = ゲート抵抗Rg・ゲート電荷Qg・寄生インダクタンスLs

- 速くする利点は「スイッチング損失減」「回路小型化」の2つ

- 速くする欠点は「サージ電圧増」「EMI悪化」「誤動作リスク」の3つ

- 2勝3敗。だから「許容範囲で最大限に速く」が正解

- 最適化は「机上→レイアウト→デバイス→定数」の順で進める

- ターンオン用とオフ用のRgは別々に設定するのが定石

「速ければ良い」は半分正解、半分ウソ。車の急ブレーキと同じで、速い操作には必ずリスクが伴います。サージ・EMI・誤動作という「副作用」を許容できる範囲で、損失が最小になる速度を見つける。これがパワエレ設計者の腕の見せどころです。

田中さんも、次にスイッチング速度の調整を任されたら、まず基板レイアウトをチェックしてみてください。寄生インダクタンスを抑えるだけで、Rgを変えなくても効率が上がることがあります。応援しています。

📚 次に読むべき記事

スイッチング速度を司るゲート駆動回路の基礎。本記事と合わせて読むと「速度設計」の全体像がつかめます。

速度の核心パラメータRgの具体的な決め方。本記事の理論をどう実値に落とすかを計算例付きで解説。

速度を決めるときに最も重視する「スイッチング損失」を理解。E_on/E_offの計算と熱設計への影響を解説。