- 設計部門が「スイッチング損失が大きいから周波数を下げよう」と話していたが、何のことかわからず黙っていた

- MOSFETのデータシートに「Eon」「Eoff」と書いてあるが、何に使うのか理解できない

- 「導通損失」と「スイッチング損失」の違いが、参考書を読んでもピンとこない

- 試作品が想定より熱くなった原因が、設計者から「スイッチング損失」と言われたが納得できない

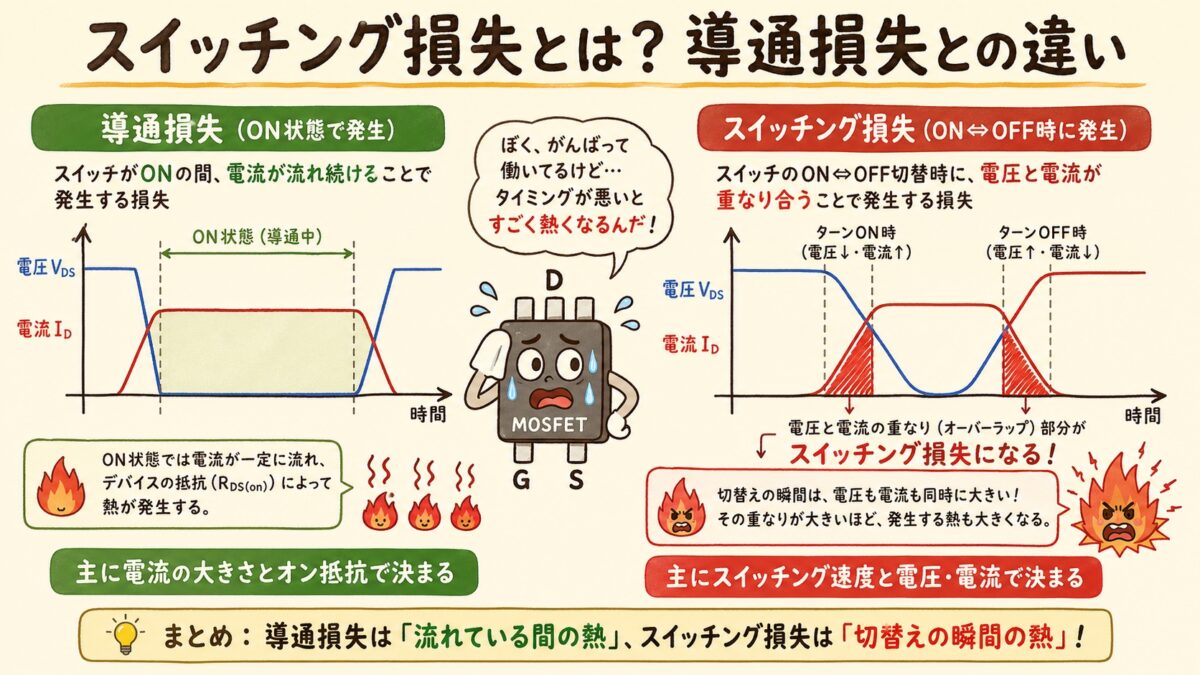

- スイッチング損失と導通損失の違いが「波形の絵」で一発理解できる

- なぜスイッチング時に損失が出るのか、その物理的メカニズムがわかる

- MOSFETでのざっくり損失計算ができるようになる

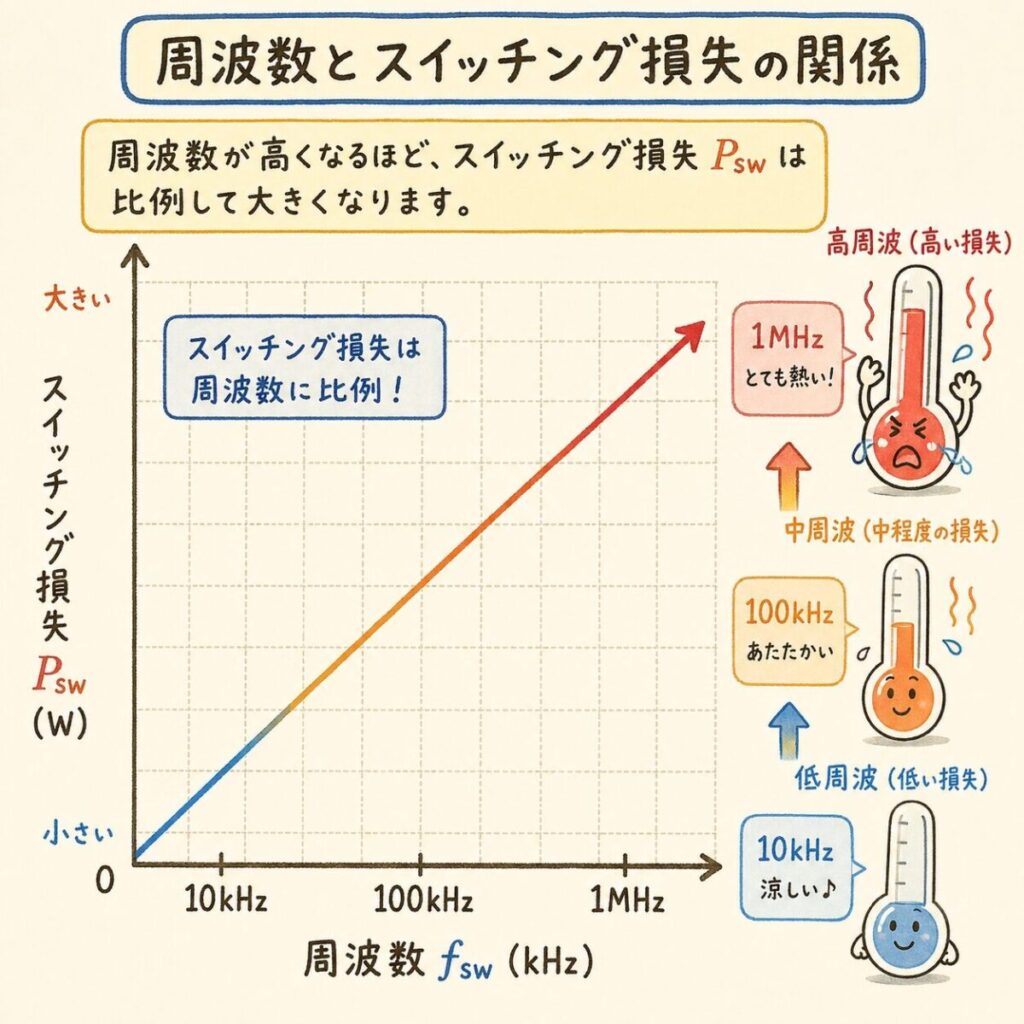

- 周波数を上げると効率が悪くなる理由を説明できるようになる

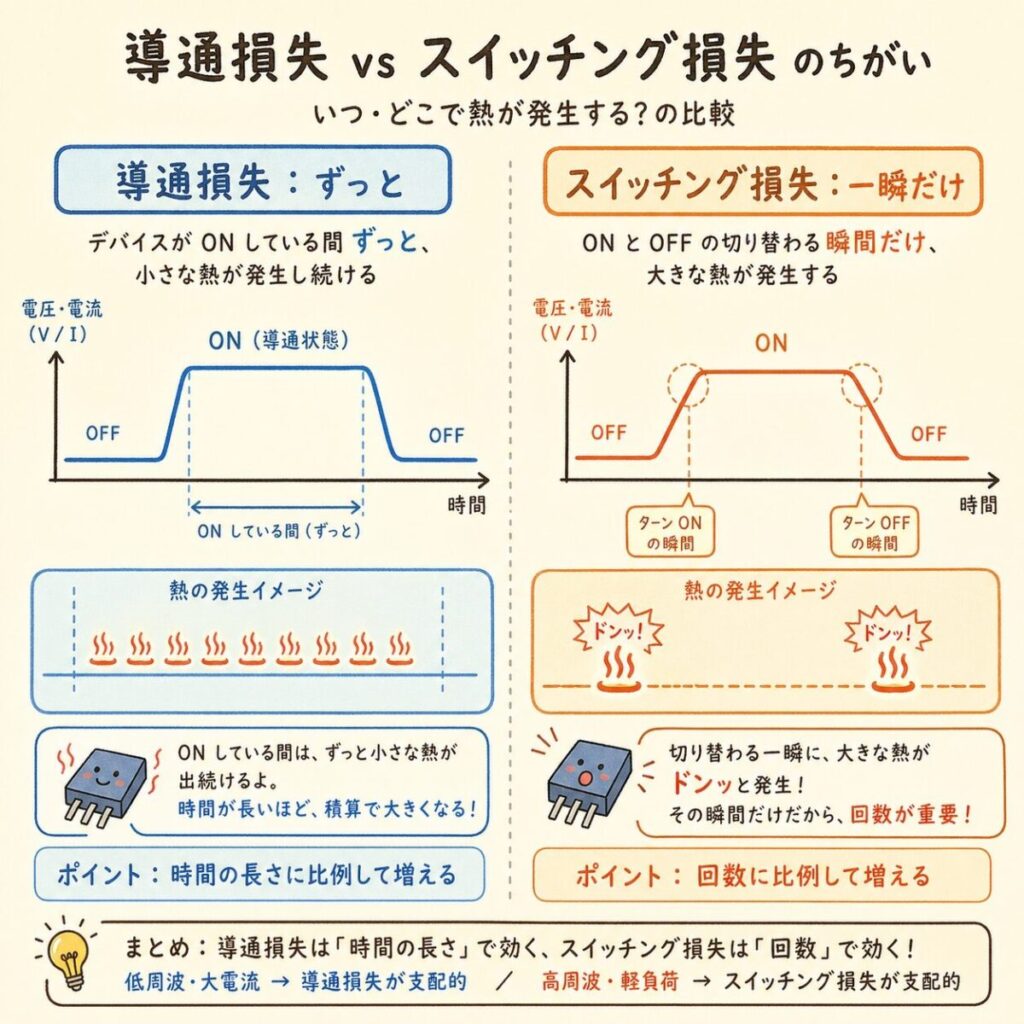

結論を先に言います。スイッチング損失とは「ON/OFFが切り替わる一瞬」に発生する熱の損失です。一方、導通損失は「ONしている間ずっと」発生する熱の損失です。両者は発生するタイミングも、計算方法も全く違います。

この記事では、なぜスイッチングのたびに損失が出るのかを波形の絵で完全に理解し、MOSFETでざっくり損失を計算できるところまで一気に解説します。読み終わる頃には、データシートの「Eon」「Eoff」「R_DS(on)」が何を意味するのか、迷わず読めるようになります。

目次

そもそもパワー素子の「損失」って何?

MOSFETやIGBTといったスイッチング素子は、理想的には「電気を100%通す」か「100%遮断する」のどちらかです。しかし現実の素子は、ONしているときも少しだけ抵抗があり、OFFに切り替わる瞬間も電圧と電流が同時にかかる時間があります。

この「電圧 × 電流 × 時間」が熱として捨てられる分が、損失です。損失は最終的にすべて熱になり、素子の温度を上げます。温度が上がりすぎると素子が壊れるので、設計者は損失を必死で減らそうとするわけです。

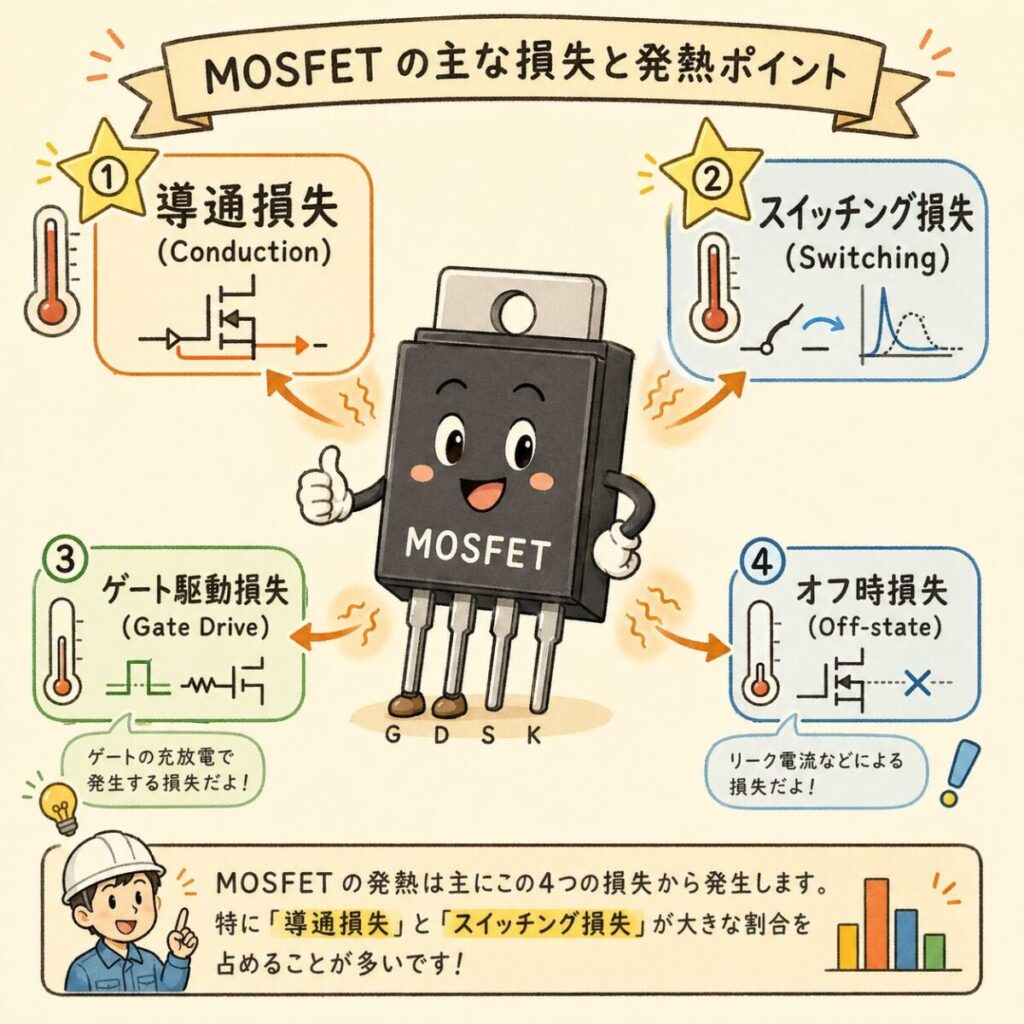

| 導通損失 | ONしている間ずっと発生(抵抗による損失) |

| スイッチング損失 | ON↔OFF切替の一瞬に発生(過渡的な損失) |

| ゲート駆動損失 | ゲートを充放電するときに発生 |

| オフ時損失 | OFF時の漏れ電流による損失(通常は無視できる) |

本記事では、このうち最も影響が大きい「導通損失」と「スイッチング損失」の2つに絞って解説します。

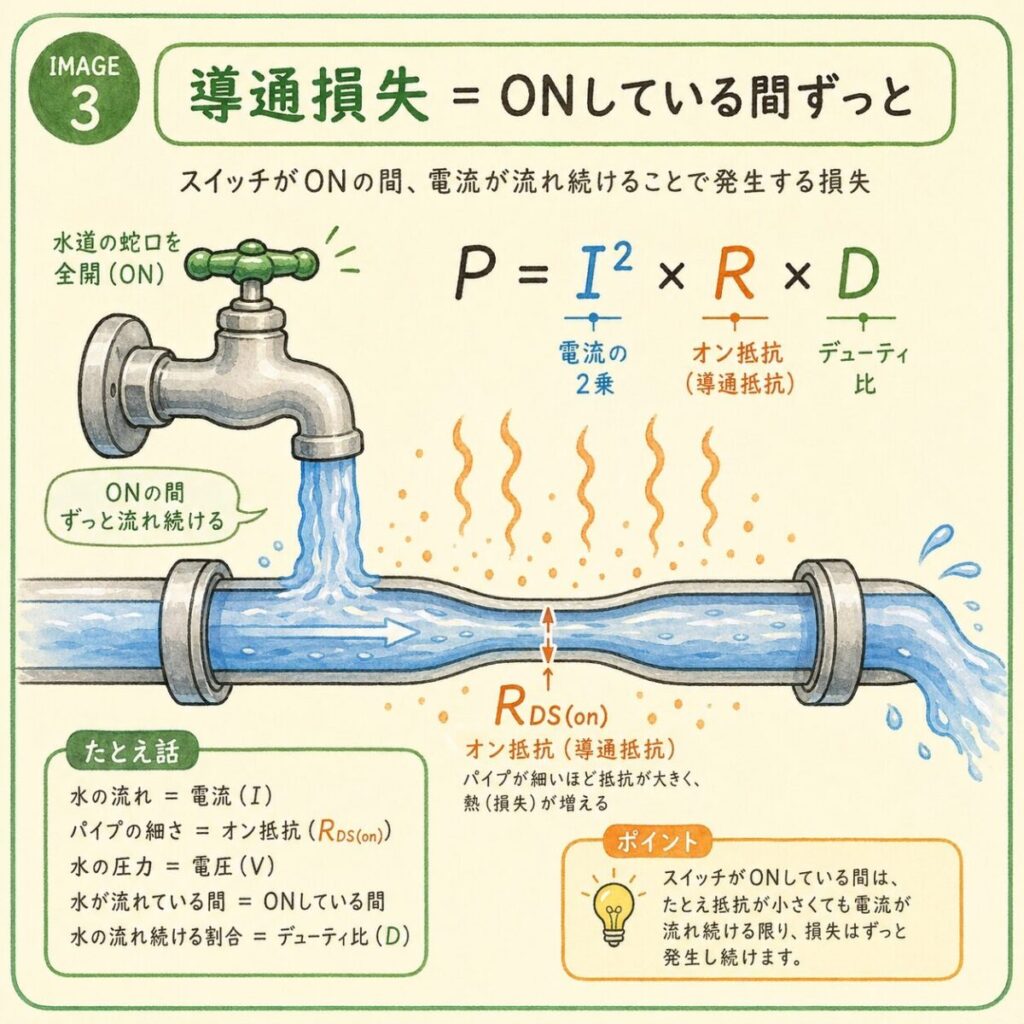

導通損失|「ONしている間ずっと出続ける熱」

導通損失(Conduction Loss)は、素子がONしている間、電流が抵抗を流れることで発生する熱です。MOSFETの場合、ON時の抵抗を「R_DS(on)」と呼びます。

P_cond = I² × R_DS(on) × D

I:流れる電流 / R_DS(on):ON抵抗 / D:デューティ比(ONしている時間の割合)

これは中学校で習ったP = I²R(ジュール熱の式)そのものです。デューティ比Dをかけているのは、「ONしている間だけ発生する」ためです。

水道の蛇口を「全開」にしているとき、パイプが少し細いと水が流れにくく、わずかに熱が発生します。これが導通損失。蛇口を開けている間ずっと発生し続ける損失です。パイプを太くする(=R_DS(on)を小さくする)と熱は減ります。

【電験三種・理論】ジュール熱とは?|Q=I²Rtで電熱線の発熱を計算する →

スイッチング損失|「切り替わる一瞬」に発生する熱

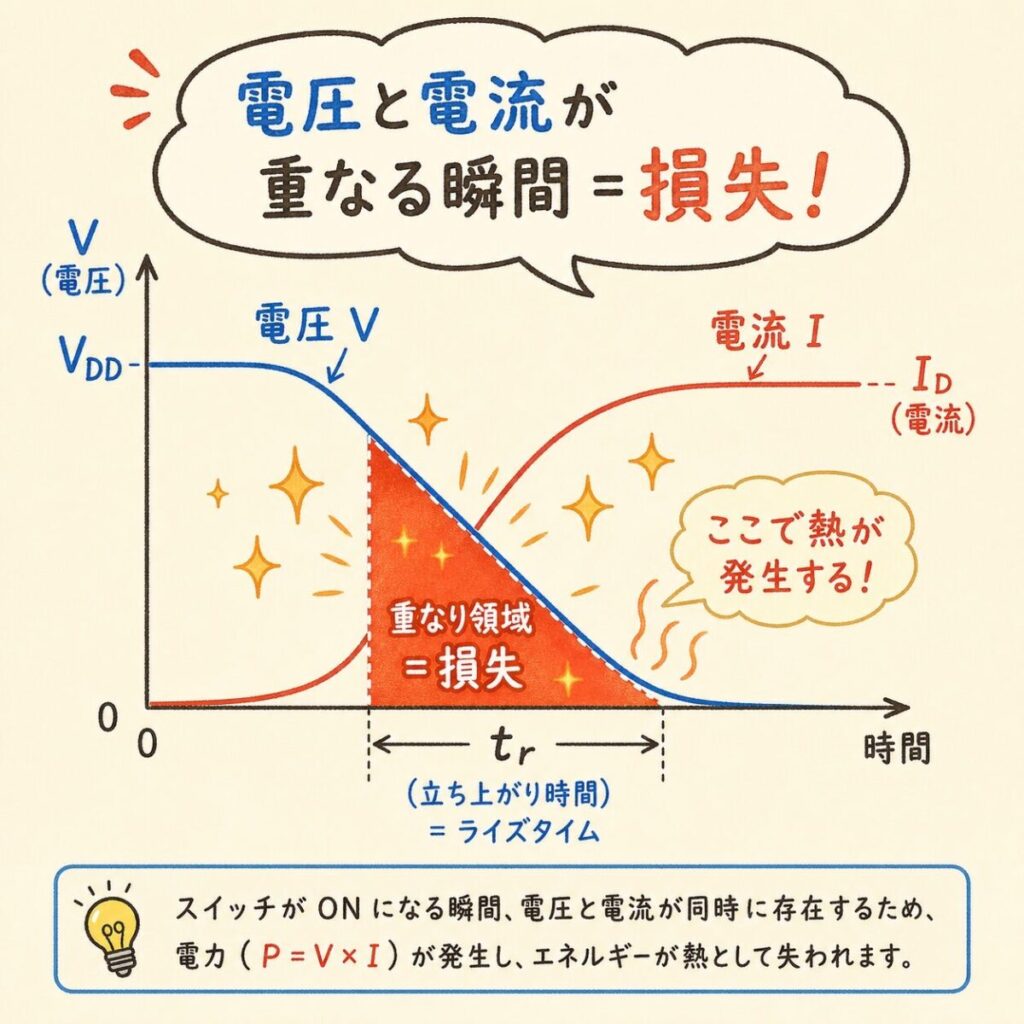

ここが本記事の核心です。スイッチング損失(Switching Loss)は、OFF→ON、ON→OFFに切り替わる「ほんの一瞬」に発生する損失です。

理想的なスイッチは、ONになる瞬間に「電圧が0V、電流が最大」へ瞬時に切り替わります。ところが現実のMOSFETは、電圧が下がりきる前に電流が流れ始めるのです。

ON切替の途中に「電圧 ≠ 0」かつ「電流 ≠ 0」の重なり時間があります。この瞬間、電圧×電流の値は瞬間的に大きな値(=瞬間電力)となり、すべて熱になります。これがスイッチング損失の正体です。

ターンオン時の波形イメージ

OFFからONへ切り替わるとき、波形は以下のように動きます。

電流が立ち上がり始める:素子に電流が流れ始めるが、電圧はまだ高いまま(=損失大)

電圧が下がり始める:電流が最大値に達した後、電圧が下がっていく(=損失中)

完全にON状態:電圧がほぼ0に。これ以降は導通損失のフェーズへ

ターンOFF時はこの逆の動きですが、やはり「電圧と電流が同時に存在する瞬間」が発生し、損失が出ます。

2つの損失の決定的な違いを比較する

ここで一旦、両者の違いを整理しましょう。

導通損失

- 発生タイミング:ON中ずっと

- 原因:素子のON抵抗

- 支配パラメータ:R_DS(on)、I

- 周波数に依存しない

- 対策:低R_DS(on)の素子を選ぶ

スイッチング損失

- 発生タイミング:切替の一瞬

- 原因:電圧と電流の波形重なり

- 支配パラメータ:t_on、t_off、V、I

- 周波数に比例して増える

- 対策:高速スイッチング素子、ゲート抵抗最適化

| 項目 | 導通損失 | スイッチング損失 |

|---|---|---|

| いつ出る? | ON中ずっと | ON↔OFFの瞬間 |

| 周波数の影響 | 影響なし | 周波数に比例 |

| 減らす方法 | 低R_DS(on)を選ぶ | 高速素子・ゲート抵抗最適化 |

| 主な計算パラメータ | R_DS(on)、I、D | V、I、t_r、t_f、f_sw |

スイッチング損失は周波数に比例して増える。これが「周波数を上げると効率が悪くなる」と言われる最大の理由です。

MOSFETのスイッチング損失をざっくり計算する

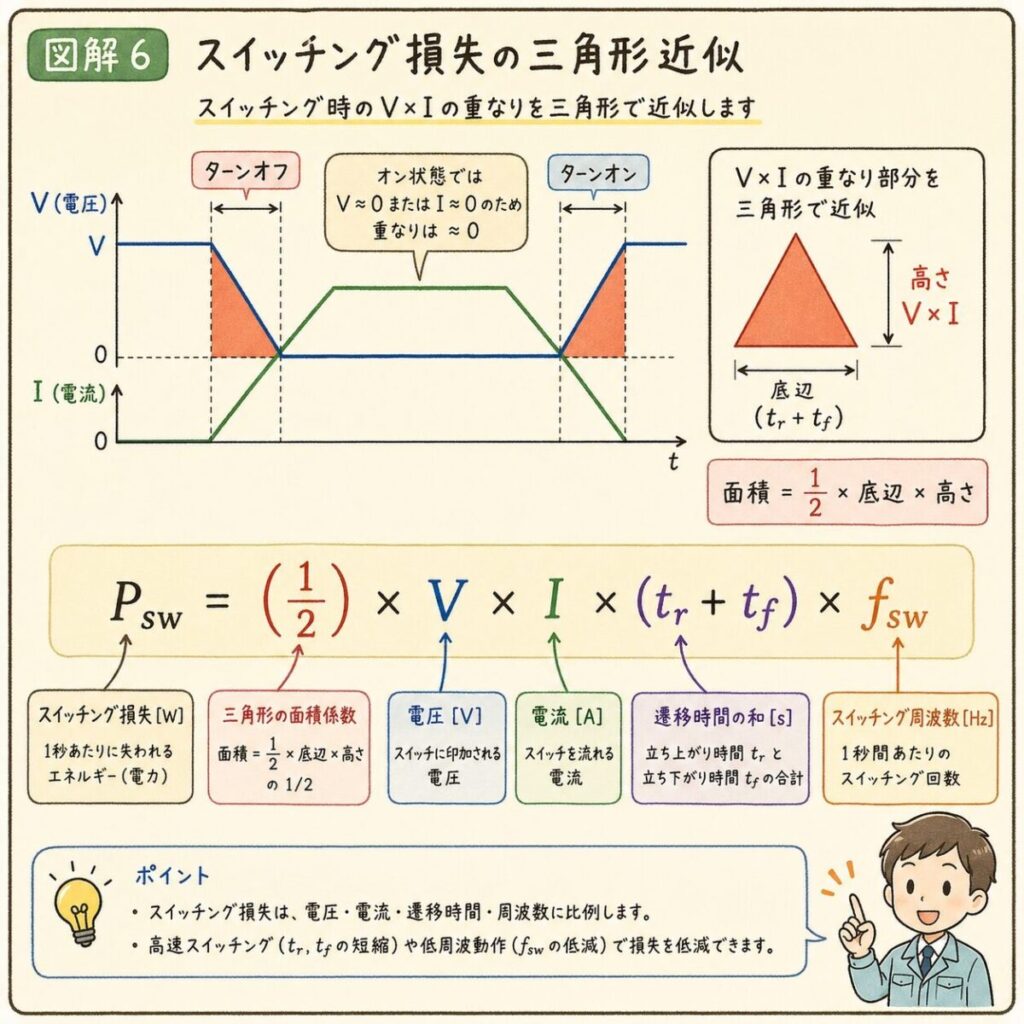

スイッチング損失を厳密に計算するには寄生容量や逆回復特性を含めた複雑な式が必要ですが、設計初期の検討では三角形近似のざっくり計算で十分です。

P_sw = (1/2) × V × I × (t_r + t_f) × f_sw

V:電源電圧 / I:負荷電流 / t_r:立上り時間 / t_f:立下り時間 / f_sw:スイッチング周波数

なぜ「1/2」がかかるのか?

スイッチング中の電圧と電流の重なりを三角形で近似するからです。三角形の面積は「底辺×高さ÷2」ですよね。底辺が時間(t_r + t_f)、高さが電圧×電流(V×I)と考えると、損失エネルギーが三角形の面積になります。

1回のスイッチング損失エネルギー:

E_sw = (1/2) × V × I × (t_r + t_f)

1秒間あたりの損失(=電力):

P_sw = E_sw × f_sw

∴ P_sw = (1/2) × V × I × (t_r + t_f) × f_sw

データシートに記載の「Eon(ターンON損失エネルギー)」「Eoff(ターンOFF損失エネルギー)」を使うと、より正確な計算ができます:

P_sw = (Eon + Eoff) × f_sw

測定条件(V_DS、I_D、R_g)が実機と異なる場合は補正が必要です。

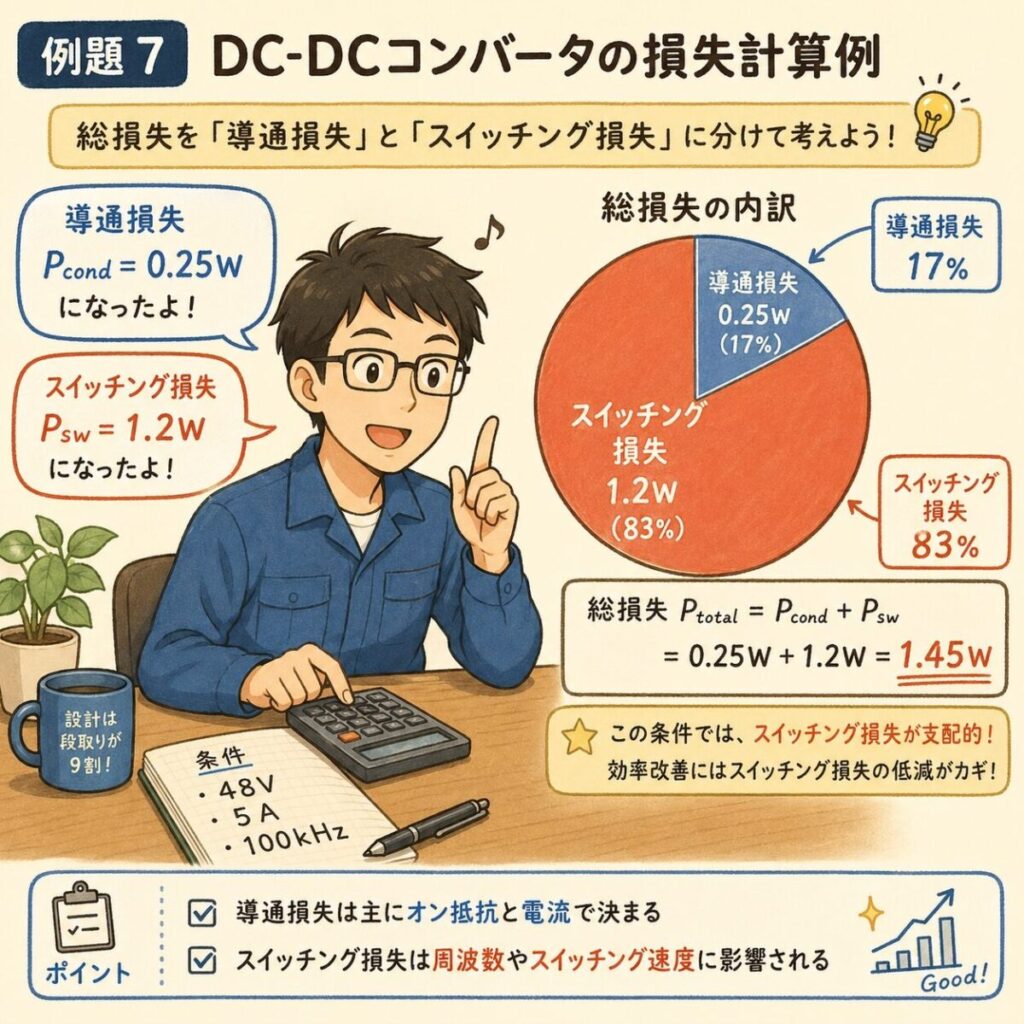

実際に計算してみる|DC-DCコンバータの例

具体的な数字を入れて、損失を計算してみましょう。

【設計条件】

- 入力電圧 V = 48V

- 負荷電流 I = 5A

- スイッチング周波数 f_sw = 100kHz

- 立上り時間 t_r = 50ns、立下り時間 t_f = 50ns

- R_DS(on) = 20mΩ

- デューティ比 D = 0.5

STEP 1:導通損失を計算

P_cond = I² × R_DS(on) × D

P_cond = 5² × 0.020 × 0.5

P_cond = 0.25W

STEP 2:スイッチング損失を計算

P_sw = (1/2) × V × I × (t_r + t_f) × f_sw

P_sw = 0.5 × 48 × 5 × (50ns + 50ns) × 100,000

P_sw = 0.5 × 48 × 5 × 100×10⁻⁹ × 100×10³

P_sw = 1.2W

STEP 3:合計損失と発見

合計損失 = P_cond + P_sw = 0.25 + 1.2 = 1.45W

→ 損失の約83%がスイッチング損失。100kHz程度でもスイッチング損失が支配的です。

「効率を上げるためにR_DS(on)が低い高級なMOSFETに変えたのに発熱が下がらない」というケース、現場でよく聞きます。原因はだいたいスイッチング損失。低R_DS(on)化は導通損失にしか効きません。スイッチング損失を減らすには、立上り/立下り時間が短い素子を選ぶ必要があります。

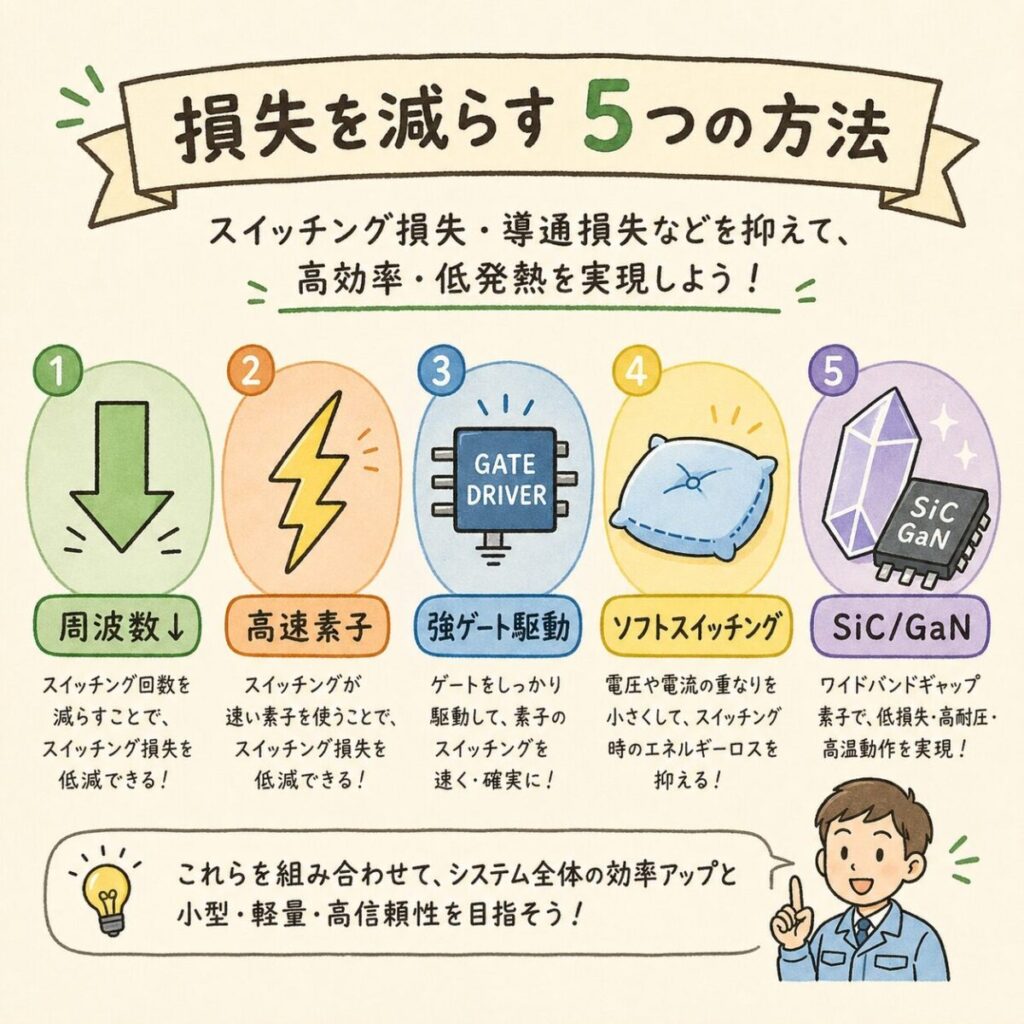

スイッチング損失を減らす5つの方法

P_sw = (1/2) × V × I × (t_r + t_f) × f_sw の式を見れば、減らす方法は自然にわかります。

スイッチング周波数 f_sw を下げる

最もシンプル。ただし周波数を下げるとインダクタやコンデンサが大きくなり、サイズが大きくなるトレードオフあり。

立上り/立下り時間を短くする

より高速なMOSFET(SiC、GaNなど)を選ぶ。ゲート抵抗を小さくしてゲート充放電を加速する。

ゲートドライブを強化する

ゲート駆動回路の能力を上げて、ゲート電圧を素早く立ち上げる。専用のゲートドライバICを使う。

ソフトスイッチング技術の採用

ZVS(ゼロ電圧スイッチング)やZCS(ゼロ電流スイッチング)を使い、電圧か電流のどちらかを0にしてから切り替える。

SiC・GaNなどのワイドバンドギャップ半導体を使う

Si MOSFETより数倍速くスイッチングできる。コストは高いが、効率改善効果は劇的。

立上り/立下り時間を短くしすぎると、サージ電圧やノイズ(EMI)が悪化します。スイッチング損失とノイズは常にトレードオフ。設計はこのバランス取りが腕の見せどころです。

ゲート抵抗の決め方|Qgから抵抗値を計算する設計手順 →

MOSFETとIGBTで損失の特徴は違う

スイッチング素子といってもMOSFETとIGBTで損失の特徴が異なります。素子選定でしばしば議論になるので押さえておきましょう。

MOSFET

- 導通損失:I² × R_DS(on)

- 低電流:効率良い

- 高電流:I²で爆増

- 高速スイッチング得意

- 適用:〜数百V、高周波

IGBT

- 導通損失:V_CE(sat) × I

- 大電流:効率良い(電流に比例)

- テール電流でスイッチング損失大

- 高速スイッチング苦手

- 適用:高電圧(600V以上)、低周波

ざっくり言えば「低電圧×高周波 = MOSFET」「高電圧×低周波×大電流 = IGBT」という棲み分けです。スイッチング損失の観点では、IGBTのほうがテール電流(ターンOFF時に電流が尾を引く現象)の影響でロスが大きくなりがちです。

【完全図解】IGBT vs MOSFETの使い分け|損失計算と選定フローチャートで「どっちを使うか」を即決する →

まとめ|「いつ・なぜ熱が出るか」を理解すれば設計が変わる

- 導通損失はON中ずっと出る損失(P = I²R × D)

- スイッチング損失はON↔OFFの一瞬に出る損失(電圧と電流の波形重なりで発生)

- スイッチング損失のざっくり式:P_sw = (1/2) × V × I × (t_r + t_f) × f_sw

- スイッチング損失は周波数に比例。高周波化すると効率が悪くなる原因

- 低R_DS(on)化は導通損失にしか効かない。発熱原因の見極めが大事

- 減らすには:周波数低減・高速素子・ゲート駆動強化・ソフトスイッチング・SiC/GaN

スイッチング損失を理解できると、「なぜこの周波数なのか」「なぜこの素子を選んだのか」という設計判断の根拠が見えてきます。設計レビューで黙らずに済むレベルになるはずです。

📚 次に読むべき記事

本記事の損失計算をどう部品選定に活かすか。実践編。

どっちを選ぶか即決できるフローチャートで判断力アップ。

スイッチング損失とノイズのトレードオフを実際に設計する手順。

本記事で学んだ損失をDC-DC設計でどう使うかの実践記事。

スイッチング損失のトレードオフ相手「サイズ」の話。

高速スイッチング化のもう一つの代償=ノイズ問題。