- パワエレ基板の部品配置、どこから手をつければいいかわからない

- 配置を終えてから「やり直し」になることが多い

- 発熱部品の配置で失敗して、熱設計がうまくいかない

- ノイズが出て原因を調べたら「配置が悪い」と言われた

- パワエレ基板で最初に決めるべき「3つの鉄則」

- 発熱部品の配置と放熱設計の基本

- 入力・出力・スイッチング部の分離方法

- 電流経路を最短化してノイズを減らすテクニック

- 具体的な配置手順とチェックリスト

「部品配置が8割」——これはパワエレ設計者の間でよく言われる格言です。

配線(ルーティング)に入る前の部品配置の段階で、基板の性能はほぼ決まります。配置がまずいと、どんなに頑張って配線しても、熱問題やノイズ問題を解決できません。

逆に言えば、部品配置さえ正しければ、配線は「つなぐだけ」で済みます。この記事では、パワエレ基板の部品配置で最初に決めるべき3つの鉄則を、具体的な手順とともに解説します。

この記事は「パワエレ基板設計の全体像」と「層構成の決め方」を理解している方向けです。

→ 【入門】パワエレ基板設計の全体像|信号基板との違いを理解する

→ 【完全図解】基板の層構成の決め方|2層・4層・6層をどう使い分けるか

目次

部品配置の3つの鉄則|これを守れば失敗しない

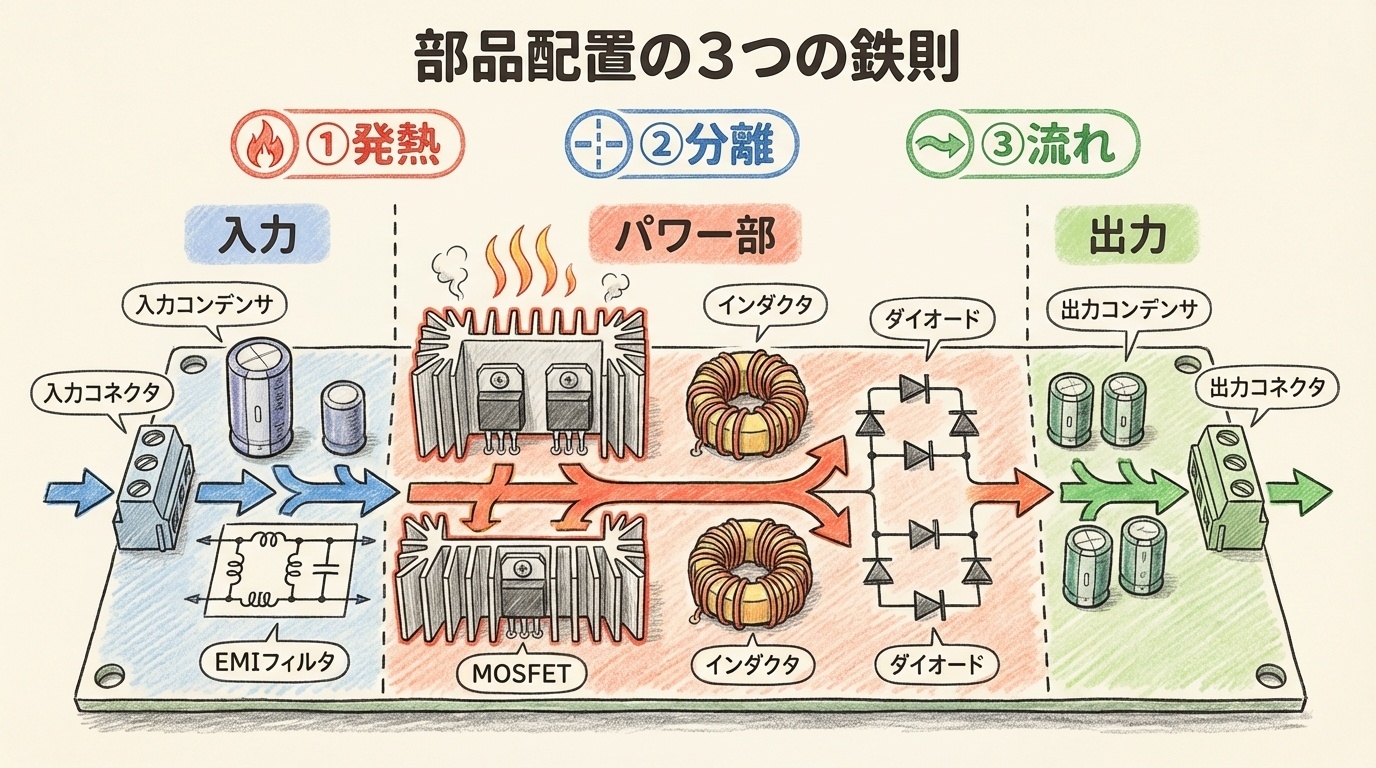

パワエレ基板の部品配置には、絶対に守るべき3つの鉄則があります。この3つを意識するだけで、配置の質は劇的に向上します。

発熱部品の配置

熱を逃がせる場所に

放熱経路を確保

入出力の分離

入力→スイッチング→出力

一方向の流れを作る

電流経路の最短化

ループ面積を最小化

ノイズの発生を抑制

この3つは優先順位の順番でもあります。まず発熱部品の配置を決め、次に入出力の分離を確認し、最後に電流経路を最適化する。この順番で考えると、手戻りが少なくなります。

・発熱部品は物理的な制約(ヒートシンク、エアフロー)が大きく、後から動かしにくい

・入出力の分離はコネクタ位置に依存し、筐体設計とも関連する

・電流経路は配置が決まれば自然と決まる部分が多い

→ 制約の大きいものから先に決めるのが鉄則

鉄則①:発熱部品の配置|熱を逃がせる場所に置く

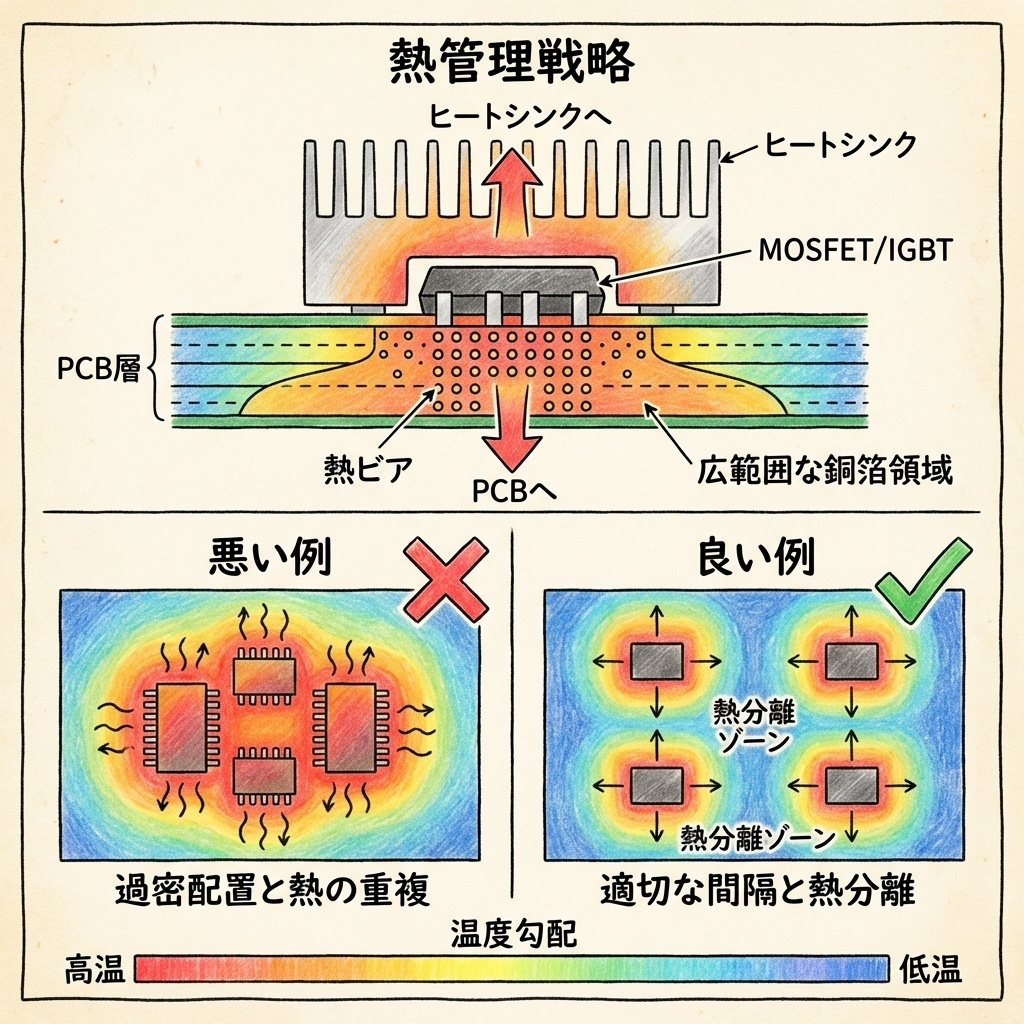

パワエレ基板で最も重要なのが、発熱部品(MOSFET、IGBT、ダイオード、インダクタなど)の配置です。これらの部品は数W〜数十Wの熱を発生させるため、適切な放熱経路を確保しないと壊れます。

発熱部品の配置で考えるべき5つのポイント

ヒートシンクの取り付けスペース

ヒートシンクを取り付ける場合、その分の高さ・面積を確保する。周囲の部品と干渉しないか確認。

エアフローの方向

ファンがある場合、風の「上流」に発熱部品を置かない。温まった空気が他の部品を加熱してしまう。

発熱部品同士の間隔

発熱部品を近くに並べると、互いの熱が干渉して温度が上昇。最低10mm以上の間隔を推奨。

基板端への配置

発熱部品は基板の端(特に筐体に接する辺)に配置すると、筐体への放熱が容易になる。

サーマルビアの配置スペース

パッド直下にサーマルビアを配置するスペースを確保。後から追加しようとしても場所がないことが多い。

発熱部品の配置パターン|良い例・悪い例

❌ 悪い配置例

🔥 熱が集中 🔥

- 発熱部品が密集している

- 熱の干渉で温度上昇

- ヒートシンクが付けられない

- 基板中央で放熱経路がない

発熱部品ごとの配置ポイント

発熱部品といっても、種類によって配置のポイントは異なります。代表的な部品ごとに解説します。

MOSFET / IGBT(パワー半導体)

| 項目 | 配置のポイント |

|---|---|

| 放熱方法 |

表面実装型(D2PAKなど):パッド直下にサーマルビアを配置 スルーホール型(TO-220など):ヒートシンクへの取付を前提に配置 |

| 推奨配置 | 基板端、またはヒートシンク直下。エアフローの上流は避ける |

| 間隔目安 | 同じヒートシンクに載せる場合でも最低5mm以上、別々なら10mm以上 |

| 注意点 | ゲートドライバICはFETの近くに配置(配線インダクタンス低減) |

パワーインダクタ / トランス

| 項目 | 配置のポイント |

|---|---|

| 発熱量 | 銅損(I²R)+鉄損で発熱。大電流品は数W〜10W以上になることも |

| 推奨配置 | エアフローが当たる位置。他の発熱部品から離す |

| 注意点 | 磁界を発生するため、制御回路(特にアナログ回路)から離す |

| 向きの考慮 | コアの向きによって磁界の漏れ方向が変わる。敏感な回路を避けて配置 |

電解コンデンサ

| 項目 | 配置のポイント |

|---|---|

| 熱の影響 | 電解コンデンサは熱に弱い。温度が10℃上がると寿命が半分に |

| 推奨配置 | 発熱部品からできるだけ離す。エアフローの下流(冷却後の空気)側に |

| 間隔目安 | MOSFET/IGBTから最低15mm以上離すのが理想 |

| 代替案 | 離せない場合は、高温対応品(105℃品など)を選定 |

電解コンデンサは「消耗品」です。周囲温度が高いと寿命が急激に短くなります。「アレニウス則」により、10℃上昇で寿命は約半分。85℃品を100℃で使うと、寿命は1/4以下になります。パワエレ基板では特に注意が必要です。

サーマルビアの配置|放熱の「裏技」

表面実装型のパワー半導体では、サーマルビアが放熱の鍵になります。パッド直下にビアを配置して、内層や裏面に熱を逃がす手法です。

🔧 サーマルビアの配置イメージ

【断面図】

サーマルビアの設計指針

| 項目 | 推奨値 | 備考 |

|---|---|---|

| ビア径 | 0.3mm〜0.5mm | 太いほど熱抵抗は下がるが、はんだ吸い込み注意 |

| ビアピッチ | 1.0mm〜1.5mm | 密に配置するほど効果的 |

| ビア数 | パッド面積に応じて最大数 | 多いほど良い。10個以上が目安 |

| ビアフィル | 樹脂充填 or 銅めっき充填 | はんだ吸い込み防止。コストは上がる |

サーマルビアを適切に配置すると、熱抵抗を30〜50%低減できることもあります。特に4層以上の基板では、内層のGNDプレーンに熱を逃がせるため効果的です。

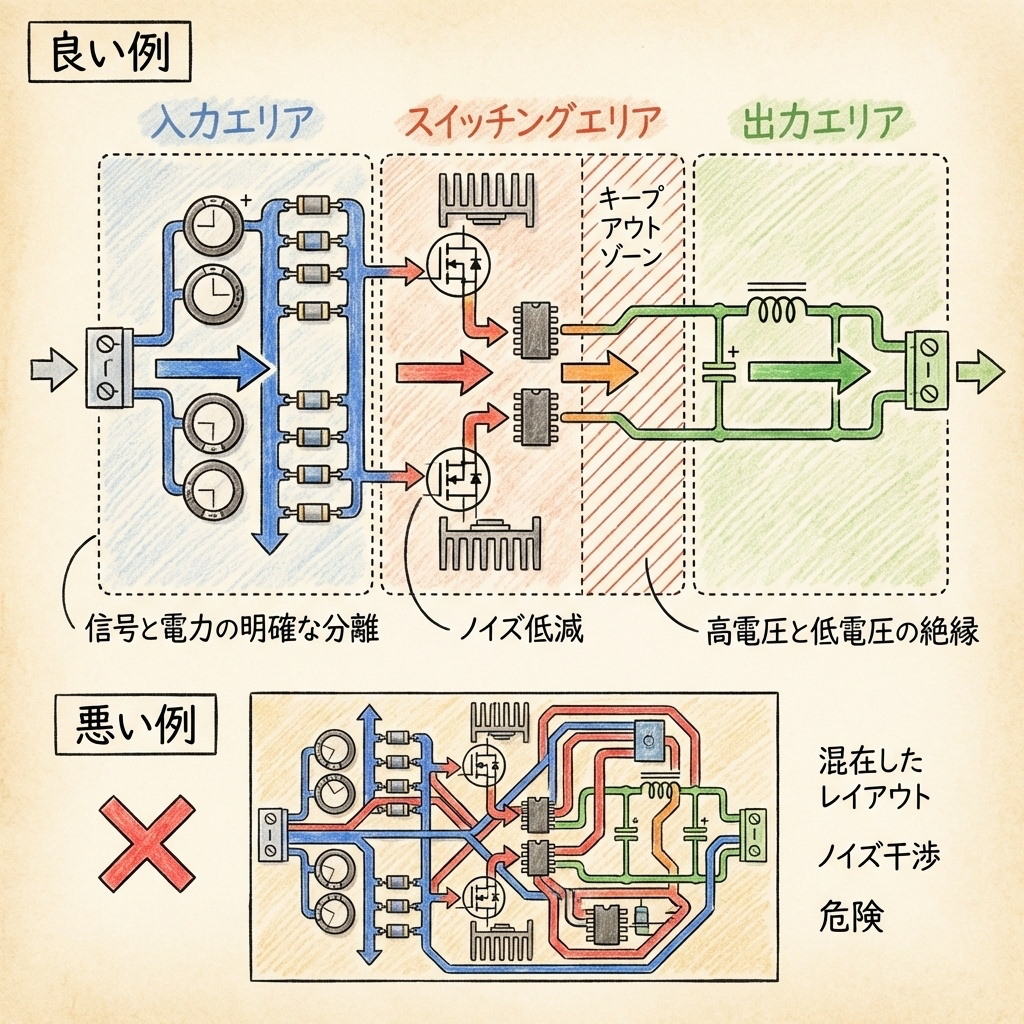

鉄則②:入出力の分離|一方向の流れを作る

パワエレ基板では、「入力→スイッチング→出力」という一方向の流れを作ることが重要です。これを「ゾーニング」と呼びます。

なぜ入出力を分離するのか?

入力と出力が混在すると、以下の問題が発生します。

🔴 ノイズの回り込み

出力のスイッチングノイズが入力側に回り込み、入力フィルタの効果が減少。EMC試験で不合格になる原因に。

🟠 GNDの電位差

大電流が流れるGNDパターンで電圧降下が発生。入力側と出力側でGND電位がずれ、制御回路が誤動作。

🔵 配線の交差

入力と出力の配線が交差すると、層数が増える原因に。ルーティングも複雑化して設計工数が増加。

基本のゾーニング|3つのエリアに分ける

パワエレ基板は、大きく3つのエリアに分けて考えます。

📐 基本のゾーニング構成

各エリアの役割と配置する部品

| エリア | 役割 | 主な部品 |

|---|---|---|

| 入力エリア | 外部からの電力を受け入れ、フィルタリング・安定化する | 入力コネクタ、EMIフィルタ、バルクコンデンサ、突入電流制限回路、ヒューズ |

| スイッチングエリア | 電力を高速でON/OFFして変換する(最もノイズが出る場所) | MOSFET/IGBT、ゲートドライバIC、スナバ回路、デカップリングコンデンサ |

| 出力エリア | 変換した電力を平滑化して外部に出力する | 出力インダクタ、出力コンデンサ、出力フィルタ、出力コネクタ |

制御回路の配置|パワー部から分離する

パワエレ基板には、スイッチングを制御するための制御回路(マイコン、PWMコントローラ、電流検出回路など)が載ることが多いです。これらは「パワー部」から分離して配置する必要があります。

📐 制御回路の配置エリア

⚡ パワー部と制御部は物理的に分離 ⚡

制御回路の配置ポイント

- パワー部から物理的に離す:最低でも10mm以上、できれば20mm以上

- GNDを分離:パワーGNDと信号GNDは1点で接続(スター接続)

- 電源を分離:制御用電源はフィルタを通してパワー部から供給

- インダクタから離す:磁界の影響を受けやすいアナログ回路は特に注意

パワーGNDと信号GNDを分離する場合、「1点で接続」するのが鉄則です。複数箇所で接続すると、パワー電流が信号GNDに回り込み、かえってノイズが増えます。接続点は入力コネクタ付近のGNDが定番です。

鉄則③:電流経路の最短化|ループ面積を最小に

パワエレ設計で最もノイズに効くのが、「電流経路(ループ)の最短化」です。電流が流れる経路の面積(ループ面積)が大きいほど、ノイズの発生・受信が増えます。

なぜループ面積が問題なのか?

電流が流れるとその周りに磁界が発生します。スイッチング回路では電流が急激に変化(dI/dt)するため、この磁界も急激に変化し、電磁ノイズ(EMI)として放射されます。

放射ノイズの強さは、ループ面積に比例します。

ループ面積を半分にすれば、ノイズも約半分に。

逆に、ループ面積が2倍になれば、ノイズも2倍に増えます。

これは「アンテナ」と同じ原理です。大きなループは大きなアンテナとなり、ノイズを効率よく放射してしまいます。

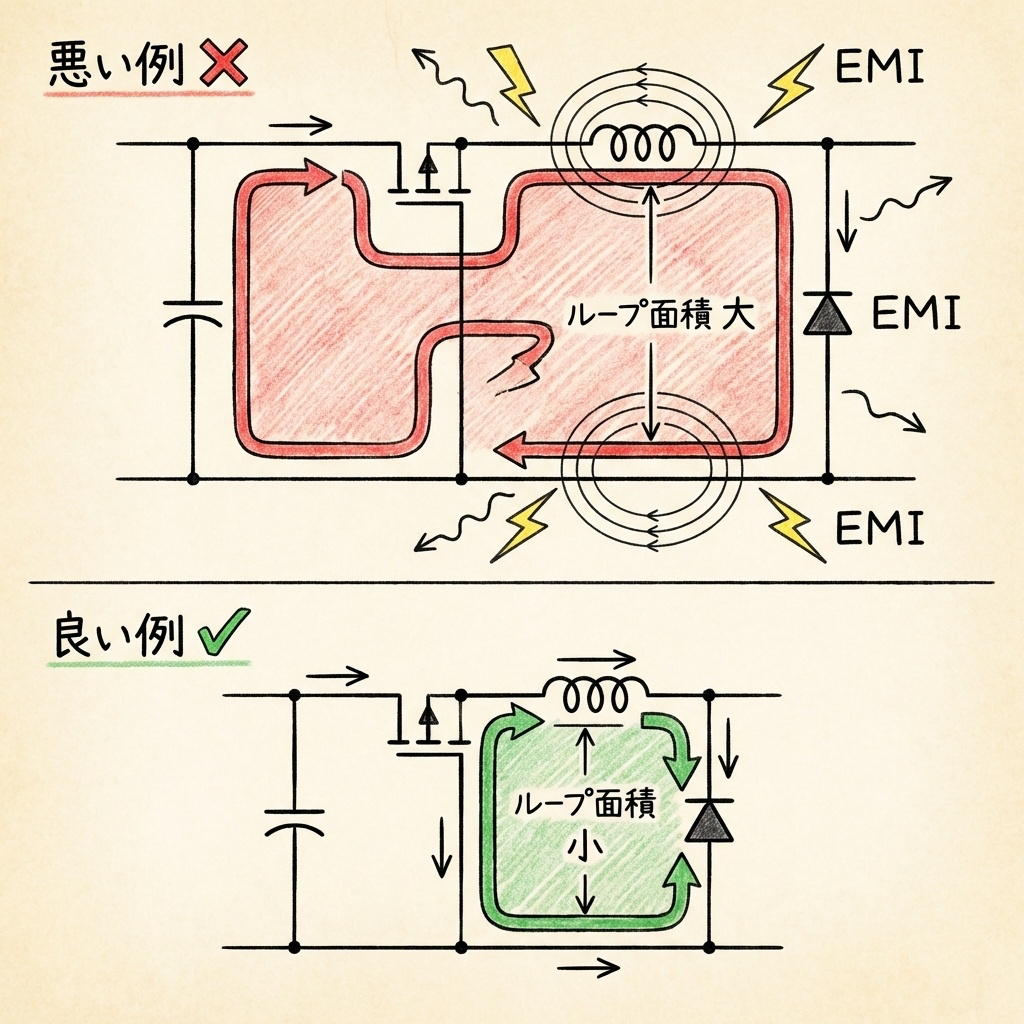

電流ループの比較|悪い例 vs 良い例

❌ 悪い例:ループ面積が大きい

- 部品が分散している

- 電流経路が遠回り

- 大きなアンテナ = ノイズ大

- EMC試験で不合格になりやすい

✓ 良い例:ループ面積が小さい

- 部品が集中している

- 電流経路が最短

- 小さなアンテナ = ノイズ小

- EMC試験に合格しやすい

重要な電流ループ|優先的に最短化すべき経路

パワエレ回路には複数の電流経路がありますが、特に高周波成分を含むループを優先的に最短化する必要があります。

① スイッチング電流ループ(最重要)

MOSFETがONするとき、入力コンデンサからMOSFETを通って戻ってくるループです。スイッチングの瞬間に大電流が急激に流れるため、最もノイズが出やすい経路です。

スイッチング電流ループの経路:

⚡ このループを最小化することが最優先 ⚡

② ゲート駆動ループ

ゲートドライバからMOSFETのゲート-ソース間を駆動するループです。このループが長いと、スイッチング速度が遅くなったり、誤動作の原因になります。

③ 出力電流ループ

出力コンデンサから負荷を通って戻ってくるループです。スイッチング電流ループほど高周波成分は多くないですが、大電流が流れるためパターン幅の確保が重要です。

① スイッチング電流ループ > ② ゲート駆動ループ > ③ 出力電流ループ

時間がない場合でも、①と②は必ず最短化してください。これだけで、EMCの問題の80%は防げます。

デカップリングコンデンサの配置|ループ最短化の鍵

スイッチング電流ループを最短化する最も効果的な方法は、デカップリングコンデンサをMOSFETの直近に配置することです。

| コンデンサ種類 | 役割 | 配置位置 |

|---|---|---|

| セラミックC (0.1μF〜10μF) |

高周波のスイッチング電流を供給 | FETの直近(5mm以内が理想) |

| 電解C (100μF〜) |

低周波のリップル電流を吸収 | 入力エリア(FETから離れてOK) |

「コンデンサは入力コネクタの近くに置く」という信号基板の常識は、パワエレには当てはまりません。

高周波デカップリング用のセラミックコンデンサは、FETのすぐ隣に置いてください。入力コネクタ近くに置いても、スイッチング電流のループは短くなりません。

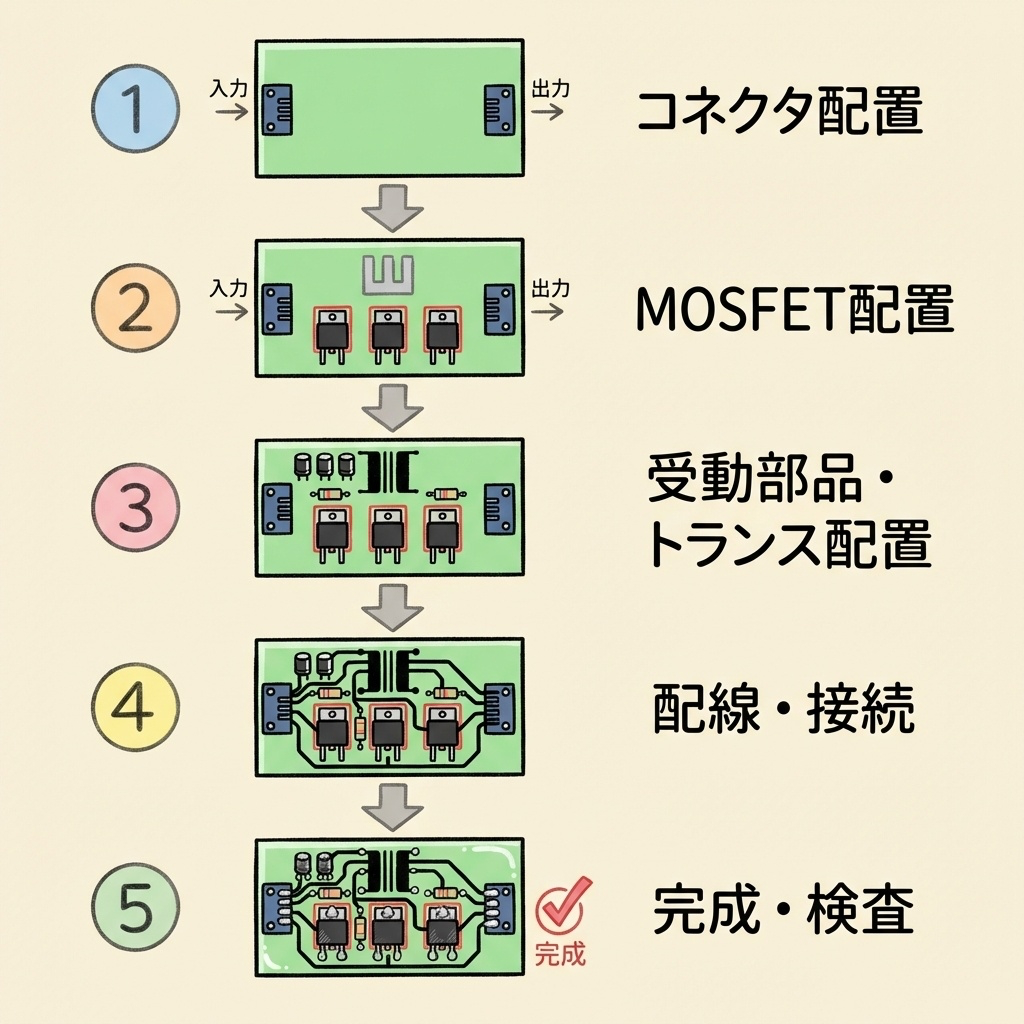

実践:部品配置の手順|5ステップで進める

ここまでの3つの鉄則を踏まえて、実際の部品配置の手順を解説します。この順番で配置すれば、手戻りが最小限になります。

コネクタを基板端に配置

入力コネクタと出力コネクタを基板の対向する辺に配置。電力の流れが一方向になるようにする。筐体設計との整合も確認。

パワー半導体を配置(発熱部品)

MOSFET/IGBTをヒートシンク取付位置に合わせて配置。発熱部品同士は離す。エアフローの方向も考慮。

デカップリングCをFET直近に配置

セラミックコンデンサをMOSFETの5mm以内に配置。スイッチング電流ループを最短化する最重要ポイント。

インダクタ・トランスを配置

電流の流れに沿って配置。制御回路から離す(磁界の影響を避ける)。エアフローが当たる位置が理想。

制御回路をパワー部から分離して配置

マイコン、PWMコントローラ、電流検出回路などをパワー部から離して配置。GNDの接続点を1箇所に決める。

部品配置チェックリスト|配線前に確認

配線(ルーティング)に入る前に、以下のチェックリストで部品配置を確認してください。配置がまずいまま配線を始めると、後で大きな手戻りになります。

✅ 部品配置チェックリスト

🔥 発熱部品(鉄則①)

- □ ヒートシンク取付スペースは確保されているか?

- □ 発熱部品同士は十分に離れているか?(10mm以上)

- □ 電解コンデンサは発熱部品から離れているか?(15mm以上)

- □ サーマルビアを配置するスペースはあるか?

- □ エアフローの上流に発熱部品を置いていないか?

🔀 入出力分離(鉄則②)

- □ 入力→スイッチング→出力の一方向の流れになっているか?

- □ 入力コネクタと出力コネクタは対向する位置にあるか?

- □ 制御回路はパワー部から分離されているか?

- □ パワーGNDと信号GNDの接続点は1箇所か?

⚡ 電流経路(鉄則③)

- □ デカップリングCはFETの5mm以内にあるか?

- □ ゲートドライバICはFETの近くにあるか?

- □ スイッチング電流ループは最短経路になりそうか?

- □ 高周波電流が流れる経路に不要な迂回はないか?

まとめ|部品配置で8割決まる

この記事では、パワエレ基板の部品配置における3つの鉄則を解説しました。

📝 この記事のまとめ

- 鉄則①:発熱部品の配置 — ヒートシンク、エアフロー、サーマルビアを考慮

- 鉄則②:入出力の分離 — 入力→スイッチング→出力の一方向の流れ

- 鉄則③:電流経路の最短化 — ループ面積を最小化してノイズを抑制

- 配置の優先順位:①発熱部品 → ②入出力分離 → ③電流経路

- デカップリングCはFETの5mm以内に配置

- 制御回路はパワー部から分離(ゲートドライバは例外)

- 配線前にチェックリストで確認して手戻りを防ぐ

部品配置が正しければ、配線は「つなぐだけ」です。逆に配置がまずいと、どんなに頑張って配線しても、熱やノイズの問題は解決できません。

「配置が8割」——この言葉を胸に、じっくり時間をかけて部品配置を検討してください。

📚 次に読むべき記事

パワエレ設計の「4大課題」をまだ読んでいない方は、こちらから全体像を把握しましょう。

部品配置の前に、層構成を決めておく必要があります。まだの方はこちらをご覧ください。

パワー半導体の種類と特徴を理解して、適切な部品選定につなげましょう。

この記事は「パワエレ基板設計 基礎編」シリーズの一部です。基礎から順番に学びたい方は、シリーズ記事をご活用ください。