😰 こんな経験ありませんか?

- ゲート波形を見たら「ギザギザ」が出ている…

- MOSFETが異常発熱する原因がわからない…

- 「リンギング」という言葉は知っているけど対策方法がわからない…

- ケルビン接続って何?普通のソースと何が違うの?

💡 この記事を読めば:リンギングの発生メカニズムから、ゲート配線の最適設計、ケルビン接続の効果まで、すべて理解できます!

📚 この記事でわかること

目次

🔔 まず知っておきたい「リンギング」とは?

ゲート波形をオシロスコープで見たとき、こんな「ギザギザ」が出ていませんか?

📊 ゲート電圧波形のイメージ

【理想波形】 【リンギング発生】

┌───────── ╭─╮

│ │ ╰╮╭╮

│ │ ╰─────

────┘ ────╯

ON ON

↑ ↑

きれいな立ち上がり 振動している!

この「振動」がリンギングです。鐘(ベル)を叩いたときに「リーン」と鳴り続けるイメージから、この名前がついています。

🚨 リンギングが引き起こす3つの問題

| 問題 | 何が起きる? | 深刻度 |

|---|---|---|

| ① 誤点弧 | OFFにしたいのに、振動でしきい値を超えてONしてしまう | 🔴 致命的 |

| ② スイッチング損失増加 | ON/OFFが不安定で、中途半端な状態が続き発熱 | 🟠 重大 |

| ③ EMI(電磁干渉) | 高周波の振動がノイズとして周囲に放射 | 🟡 要注意 |

⚠️ 特に危険なのは「誤点弧」

ハーフブリッジ回路で誤点弧が起きると、上下のMOSFETが同時ONしてアーム短絡→素子破壊の最悪シナリオに…

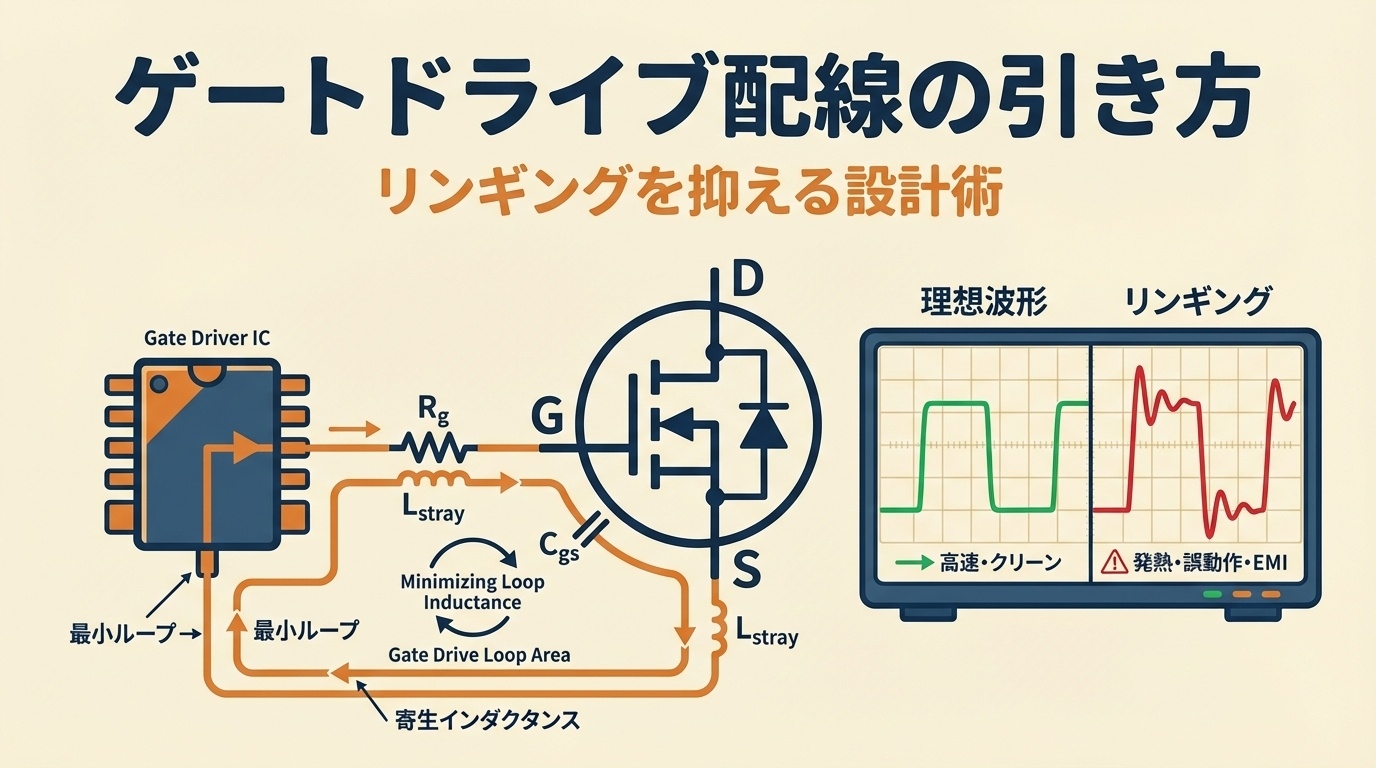

🔬 リンギングの正体は「LC共振」

リンギングの原因は、ゲート配線に存在する寄生インダクタンス(L)とゲート容量(C)が作るLC共振回路です。

🎸 ギターの弦で例えると…

🎵 ギターの弦

弦を弾く→振動が続く

(弦の張力とバネ性で共振)

⚡ ゲート回路

スイッチング→電圧が振動

(LとCで共振)

📐 共振周波数の公式

f = 1 / (2π√LC)

L = 配線の寄生インダクタンス、C = ゲート容量

つまり、リンギングを減らすには「L」を減らすことが最重要!これがこの記事の核心です。

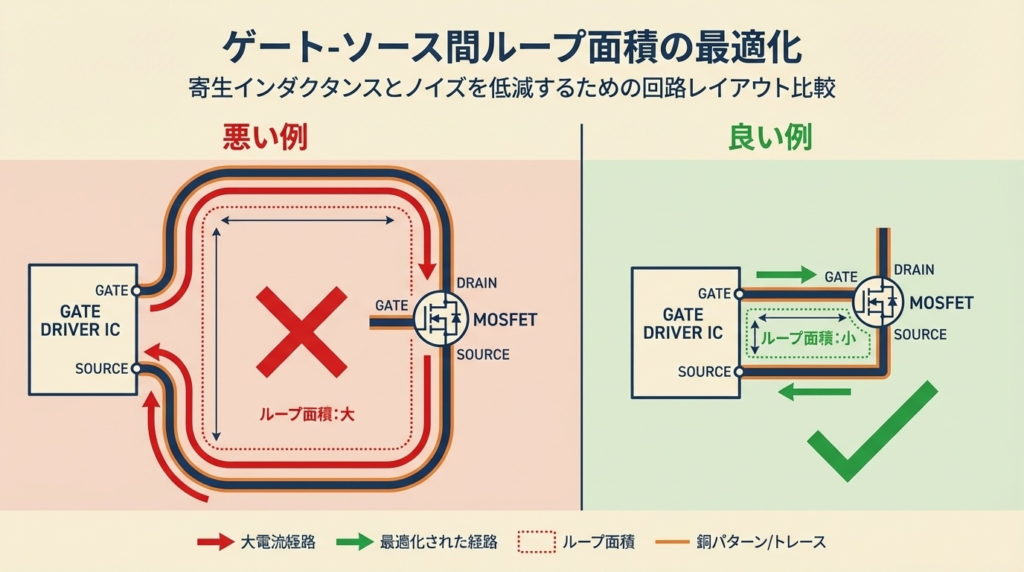

🔄 対策①:ゲート・ソース間ループ面積を最小化する

リンギングを抑える最も効果的な方法は、ゲート電流が流れるループの面積を小さくすることです。

📏 なぜ「面積」が重要なのか?

配線の寄生インダクタンスは、ループ面積に比例します。

📐 寄生インダクタンスの関係

L ∝ ループ面積 / 配線間隔

面積が2倍 → インダクタンスも約2倍 → リンギングが悪化

❌ 悪い例:ループが大きい

┌──────────────────────┐ │ ゲートドライバIC │ └──────────┬───────────┘ │ ゲート配線 │ (長い!) │ ↓ ┌─────────┐ │ MOSFET │ └────┬────┘ │ ソース配線 (また長い!) │ ↓ ──────────────────── GND

⚡ ループ面積が大きい

⚡ 寄生インダクタンス大

⚡ リンギング発生!

✅ 良い例:ループが小さい

┌─────────────┐ │ ドライバIC │ └──┬──────┬──┘ │ │ │G │S(近い!) │ │ ┌─┴──────┴─┐ │ MOSFET │ └───────────┘

✓ ループ面積が小さい

✓ 寄生インダクタンス小

✓ リンギング抑制!

🛠️ ループ面積を小さくする5つのテクニック

💡 設計目安

ゲート・ソース間のループ面積は10mm²以下を目標にしましょう。

これは約「3mm × 3mm」の正方形に相当します。

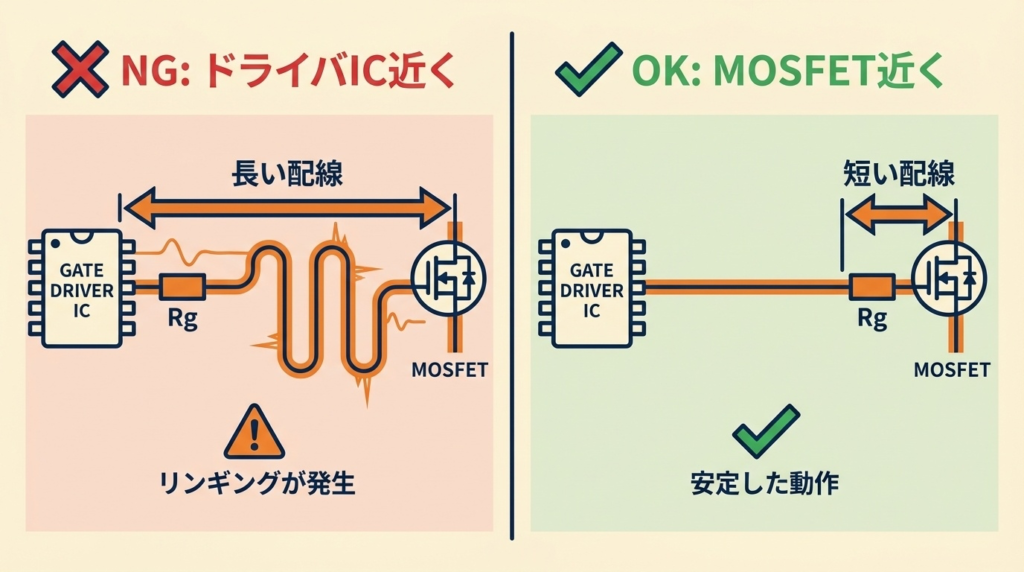

⚡ 対策②:ゲート抵抗の正しい配置場所

ゲート抵抗の「値」だけでなく、「配置場所」がリンギング対策に大きく影響します。

🤔 ゲート抵抗の役割をおさらい

ゲート抵抗は、LC共振回路における「ダンパー」の役割を果たします。

🚗 車のショックアブソーバーで例えると…

|

🚙 車の場合 段差を越える→バネだけだと揺れ続ける→ショックアブソーバーで振動を吸収 |

⚡ ゲート回路の場合 スイッチング→LCで振動しようとする→ゲート抵抗で振動を減衰 |

📍 配置場所の鉄則:MOSFETゲート端子の直近!

結論から言うと、ゲート抵抗は「MOSFET側」に配置するのが正解です。

❌ NG:ドライバIC側に配置

┌─────────┐

│ドライバIC├─[Rg]─────長い配線─────┬─G

└─────────┘ │

┌──┴───┐

│MOSFET│

└──────┘

❌ Rgより後ろの配線でリンギング発生

❌ ダンピング効果が届かない

✅ OK:MOSFET側に配置

┌─────────┐

│ドライバIC├─────長い配線─────[Rg]─┬─G

└─────────┘ │

┌──┴───┐

│MOSFET│

└──────┘

✓ Rgがゲート直前で振動を吸収

✓ ダンピング効果が最大限発揮

💡 なぜMOSFET側なのか?

ゲート抵抗は、その後ろ側のインダクタンスに対してしかダンピング効果がありません。

ドライバIC側に配置すると、「ゲート抵抗〜MOSFET間の配線」でリンギングが発生してしまいます。

MOSFET直近に配置すれば、配線のほぼ全体に対してダンピングが効きます。

📊 ゲート抵抗値の選定ガイド

| 抵抗値 | スイッチング速度 | リンギング | スイッチング損失 |

|---|---|---|---|

| 小さい (1〜5Ω) |

⚡ 速い | 📈 多い | 📉 少ない |

| 大きい (10〜47Ω) |

🐢 遅い | 📉 少ない | 📈 多い |

トレードオフの関係にあるため、用途に応じて最適値を選ぶ必要があります。

💡 一般的な推奨値

| Si MOSFET | 4.7〜22Ω |

| GaN FET | 0〜10Ω(高速性重視の場合は低め) |

| IGBT | 10〜47Ω(大容量のため) |

🔧 ON/OFF別抵抗(分離ゲート抵抗)

より細かい制御を行いたい場合、ONとOFFで別々のゲート抵抗を使う手法があります。

⚙️ 分離ゲート抵抗の構成

┌──[Rg_on]──→──┐

ドライバIC ──┤ ├── Gate

└──[Rg_off]─←─┘

↑

ダイオードで

電流方向を分離

Rg_on:小さめ(高速ON)

Rg_off:大きめ(リンギング抑制・ソフトOFF)

⚠️ 注意:分離ゲート抵抗を使う場合も、必ずMOSFET直近に配置してください。

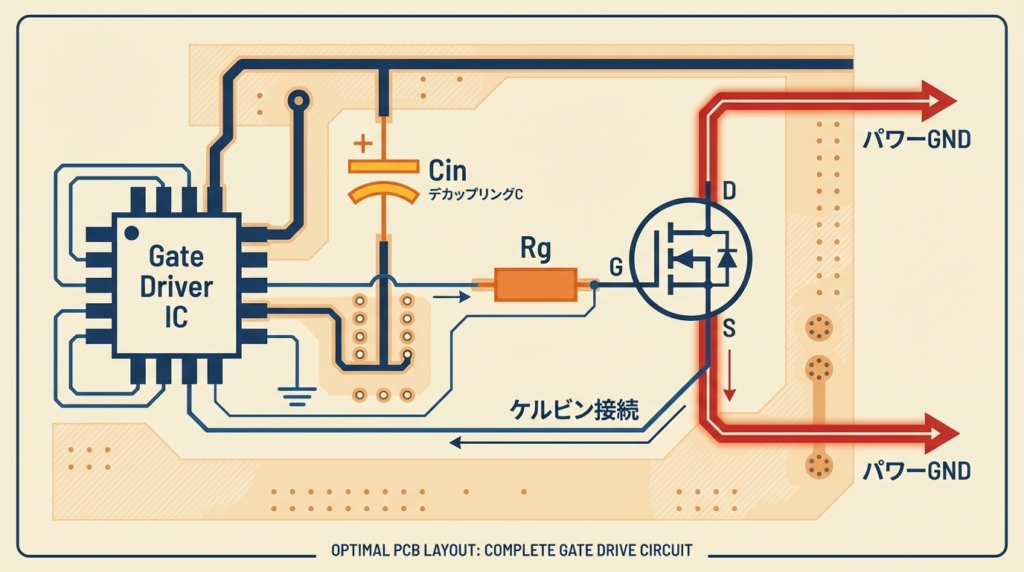

🔗 対策③:ケルビン接続(ケルビンソース)を活用する

「ケルビン接続」は、リンギング対策の切り札とも言える手法です。最近のMOSFETパッケージには、この機能が搭載されていることが多くなっています。

🤔 そもそも「ケルビン接続」とは?

ケルビン接続とは、電流測定や電圧検出で使われる「4端子接続」の考え方をMOSFETに応用したものです。

📏 ケルビン接続の由来

抵抗値を高精度で測定する「4端子法」は、19世紀の物理学者ケルビン卿(Lord Kelvin)が考案しました。

「電流を流す経路」と「電圧を測る経路」を分けることで、配線抵抗の影響を排除する手法です。

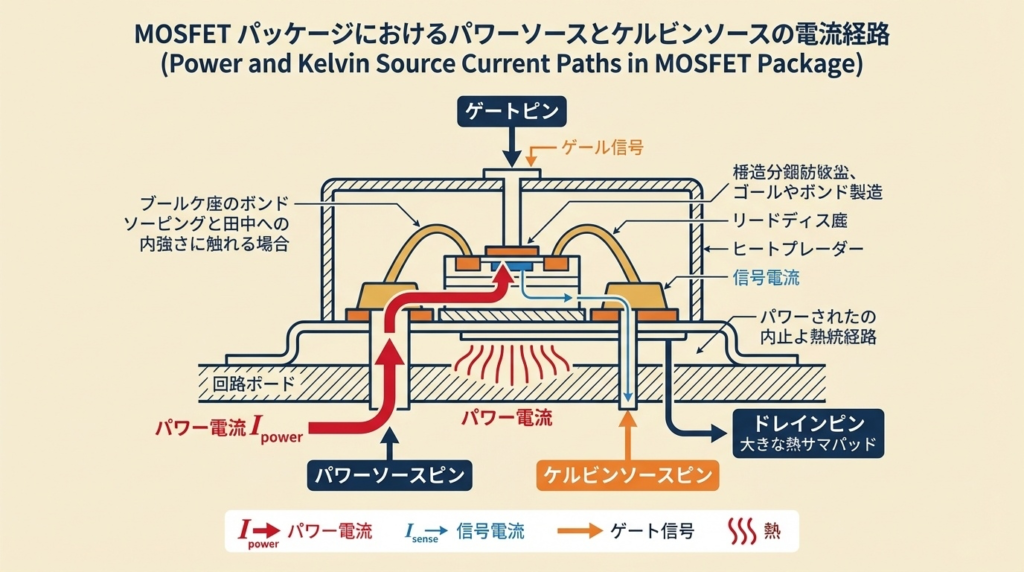

⚡ MOSFETにおけるケルビンソース

MOSFETパッケージでは、「パワーソース」と「ケルビンソース」の2つのソース端子を持つものがあります。

🔴 パワーソース(S)

- 大電流が流れる

- 主回路電流の帰還経路

- 数十A〜数百A

🟢 ケルビンソース(SS, SE)

- 微小電流のみ

- ゲート駆動の基準点

- 数mA〜数十mA

❓ なぜソースを分離する必要があるのか?

パワーソースには大電流が流れるため、配線やボンディングワイヤに寄生インダクタンスが存在します。

🚨 パワーソースを基準にした場合の問題

┌───────────────────┐

│ MOSFET内部 │

│ │

Gate ──────┤G │

│ ┌───┐ │

│ │ SW │ │

│ └─┬─┘ │

│ Ls │ │

│ (寄生)│ │

Source ────┼───L───┘ │

│ ↑ │

│ この電圧降下が │

│ ゲート電圧に影響!│

└───────────────────┘

V = Ls × dI/dt で電圧が発生

→ ゲート電圧が変動

→ リンギングの原因に!

✅ ケルビンソースを基準にした場合

┌───────────────────┐

│ MOSFET内部 │

│ │

Gate ──────┤G │

│ ┌───┐ │

│ │ SW │ │

│ └─┬─┘ │

│ ├──────────┼── Kelvin Source (SS)

│ Ls │ │ ↑

│ (寄生)│ │ ゲート駆動はここを基準

│ │ │

Source ────┼───L───┘ │

│ ↑ │ パワー電流はこちら

│ パワー電流のみ │

└───────────────────┘

ゲート回路とパワー回路が分離!

→ dI/dtの影響を受けない

→ リンギング大幅改善!

📊 ケルビン接続の効果(実測データ)

| 項目 | 通常接続 | ケルビン接続 | 改善率 |

|---|---|---|---|

| リンギング振幅 | ±5V | ±1V | 80%減 |

| ターンオン時間 | 50ns | 35ns | 30%高速化 |

| スイッチング損失 | 基準 | -15% | 15%減 |

※効果は条件により異なりますが、一般的にケルビン接続は非常に有効です。

📦 ケルビンソース搭載パッケージ

| パッケージ名 | メーカー例 | ケルビン端子名 |

|---|---|---|

| TO-247-4 | Infineon, ROHM | SS(Sense Source) |

| D2PAK-7 | STMicro | SE(Source Emitter) |

| TOLL | Infineon | SS |

| QDPAK / DDPAK | 各社 | SS / Kelvin Source |

💡 選定のポイント

新規設計では、可能な限りケルビンソース端子付きパッケージを選定しましょう。

特にSiC MOSFETやGaN FETなど、高速スイッチングが求められるデバイスでは必須級の機能です。

📋 設計チェックリスト

これまでの内容を実際の設計で確認できるチェックリストにまとめました。

📝 この記事のまとめ

リンギング = LC共振

配線の寄生インダクタンス(L)とゲート容量(C)が原因。Lを減らすことが最重要。

ループ面積を最小化

ゲート・ソース間のループ面積は10mm²以下を目標。ドライバIC直近配置、配線並走がカギ。

ゲート抵抗はMOSFET直近に

ドライバIC側ではなく、MOSFET側に配置することでダンピング効果を最大化。

ケルビン接続を活用

パワーソースとケルビンソースを分離することで、dI/dtの影響を排除しリンギングを大幅改善。

⚠️ 忘れないで!

リンギング対策は、回路図上では見えない「パターン設計」の領域です。回路図が正しくても、基板設計が悪ければリンギングは発生します。早い段階から基板レイアウトを意識した設計を心がけましょう。

📚 次に読むべき記事

【図解】スイッチングノイズはなぜ出る?|ループ面積と dI/dt の関係

→ ノイズ発生のメカニズムをさらに深く理解

【図解】ノイズを減らすパターン設計|電流ループ面積を最小化する配置

→ 部品配置の観点からさらにノイズ対策を強化

【完全図解】パワーエレクトロニクスに必要な周辺回路まとめ

→ スナバ回路、保護回路など全体像を把握

💡 リンギングは「見えない敵」ですが、

正しい知識と設計手法で必ず制御できます。

この記事が、あなたのパワエレ設計のお役に立てれば幸いです!