- 「V = L × dI/dt」の式、見たことはあるけど意味がわからない…

- なぜ配線が長いとサージが大きくなるの?

- 基板設計でサージを減らすには、具体的に何をすればいい?

- 配線インダクタンスがサージ電圧を生む「物理的な理由」

- V = L × dI/dt の式を水道管で直感的に理解

- サージを減らすための具体的な設計テクニック

これまでのスナバ回路シリーズでは、サージを「吸収する」方法を解説してきました。RCスナバ、RCDスナバ、アクティブクランプ、TVSダイオード…どれも「発生したサージをどう処理するか」という視点でした。

しかし、本当に大切なのは「そもそもサージを発生させない」ことです。サージの発生量を減らせれば、スナバ回路の負担も軽くなり、効率も上がります。

そのためには、サージが発生する「根本原因」を理解する必要があります。その答えが、今回のテーマである「配線インダクタンス」と「V = L × dI/dt」の式です。

スナバ回路が「治療」だとすれば、この記事は「予防」の話です。サージの発生メカニズムを理解することで、設計段階からサージを最小化できるようになります。

目次

インダクタンスとは何か?

まず、「インダクタンス」という概念を直感的に理解しましょう。

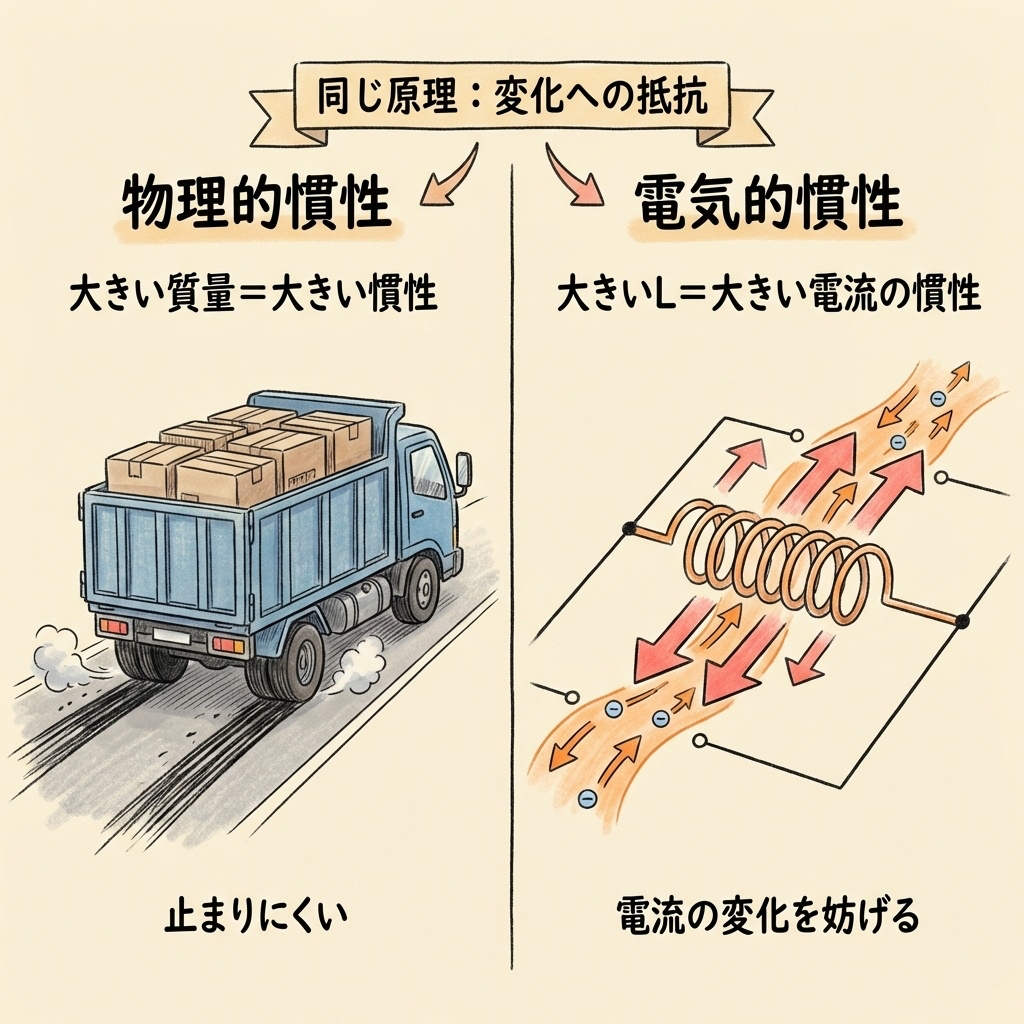

インダクタンス = 電流の「慣性」

インダクタンス(L)は、「電流の変化を妨げる性質」です。物理学でいう「慣性」と同じようなものだと考えてください。

物体の慣性(質量)

- 重い物体は動き出しにくい

- 重い物体は止まりにくい

- 急に止めようとすると大きな力が必要

電流の慣性(インダクタンス)

- 電流は急に流れ出しにくい

- 電流は急に止まりにくい

- 急に止めようとすると大きな電圧が発生

インダクタンスが大きいほど、電流の変化に対する「抵抗感」が強くなります。そして、無理やり電流を変化させようとすると、その「反発」として電圧が発生します。これがサージ電圧の正体です。

配線にもインダクタンスがある

「インダクタンス」と聞くと、コイル(インダクタ)を思い浮かべるかもしれません。しかし、実はすべての配線にはインダクタンスがあるのです。

- プリント基板のパターン:約 10 nH/cm

- リード線・ジャンパー線:約 10〜20 nH/cm

- ボンディングワイヤ:約 1 nH/mm

「たった10nH」と思うかもしれませんが、高速スイッチングでは無視できない値になります。

この「配線のインダクタンス」を「寄生インダクタンス」や「ストレーインダクタンス」と呼びます。意図せず存在するインダクタンスという意味です。

寄生インダクタンスは回路図には現れません。しかし、実際の基板には必ず存在し、サージやノイズの原因になります。「回路図では動くはずなのに、実機では壊れる」という問題の多くは、この寄生インダクタンスが原因です。

V = L × dI/dt の意味を理解する

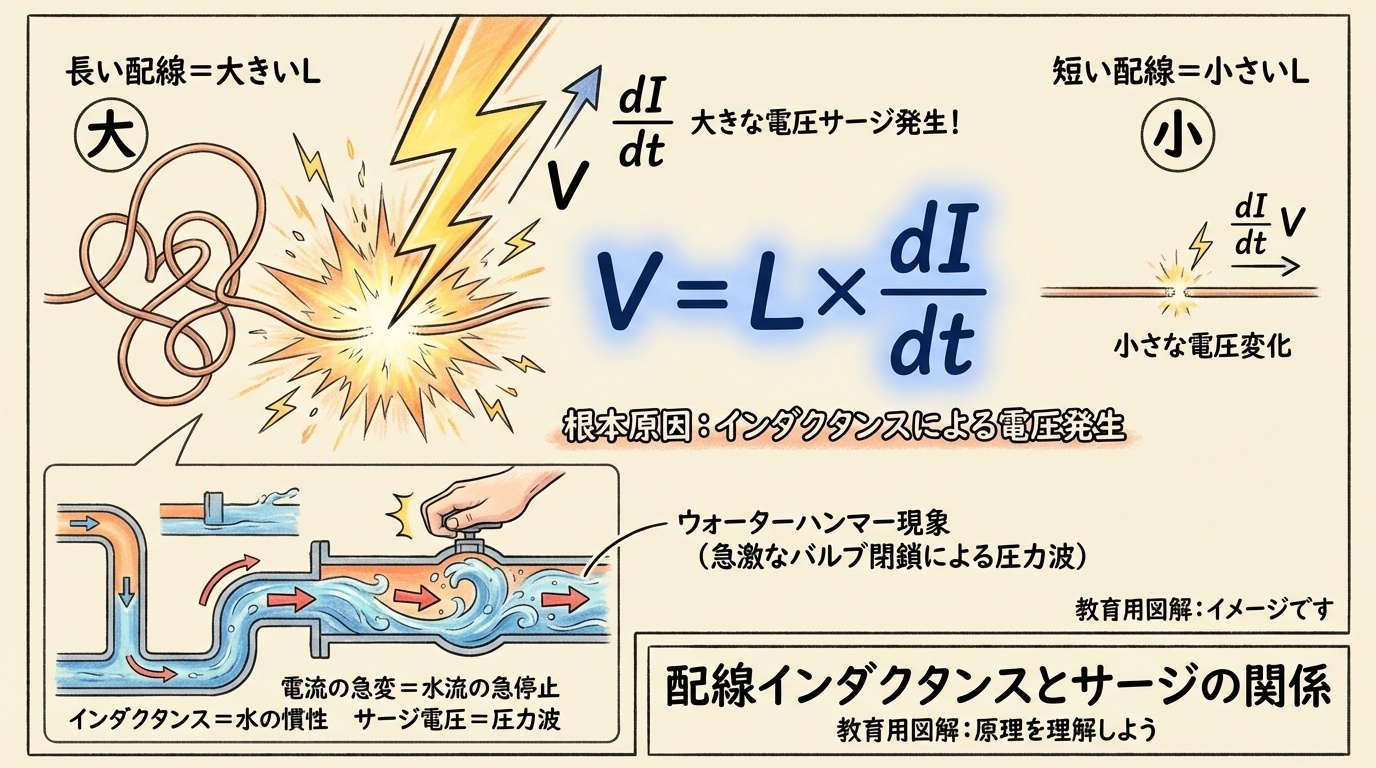

サージ電圧を支配する最も重要な式が、V = L × dI/dt です。この式の意味を、水道管で例えて理解しましょう。

式の意味

この式は、「インダクタンスが大きいほど」または「電流の変化が急激なほど」、サージ電圧が大きくなることを示しています。

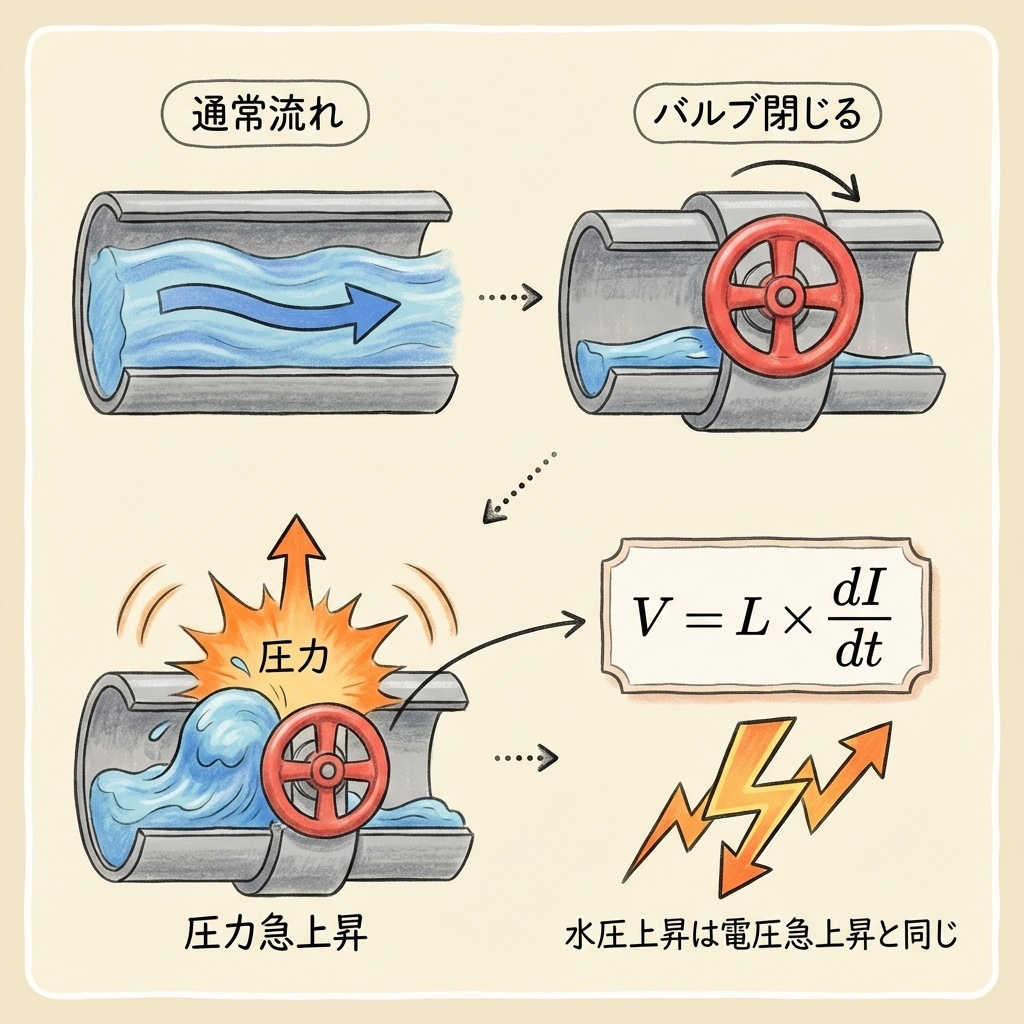

水道管の「ウォーターハンマー」で理解する

V = L × dI/dt は、水道管の「ウォーターハンマー現象」と全く同じ原理です。

🚿 ウォーターハンマー現象とは?

蛇口を急に閉めると、「ドン!」という衝撃音がすることがありますよね。これは、流れていた水が急に止められたことで、水の慣性によって圧力スパイク(衝撃波)が発生する現象です。

電気回路でも全く同じことが起きています。

水道管

水の流れ = 電流

管の長さ・太さ

水の慣性 = インダクタンス L

蛇口を閉める速さ

流れの変化率 = dI/dt

衝撃波(ドン!)

圧力スパイク = サージ電圧 V

3つのシナリオで比較

| シナリオ | 水道管で例えると | 電気回路では | サージ |

|---|---|---|---|

| 短い管 × ゆっくり閉める | 小さい慣性 × 緩やかな変化 | 小さいL × 小さいdI/dt | 小 |

| 長い管 × ゆっくり閉める | 大きい慣性 × 緩やかな変化 | 大きいL × 小さいdI/dt | 中 |

| 長い管 × 急に閉める | 大きい慣性 × 急激な変化 | 大きいL × 大きいdI/dt | 大! |

V = L × dI/dt の式から、サージを減らすには2つのアプローチがあることがわかります:

① L を小さくする:配線を短くする、ループ面積を小さくする

② dI/dt を小さくする:スイッチングを遅くする(ただしスイッチング損失が増加)

具体的な計算例

V = L × dI/dt を使って、実際にサージ電圧を計算してみましょう。数字を入れると、配線インダクタンスの影響がいかに大きいかがわかります。

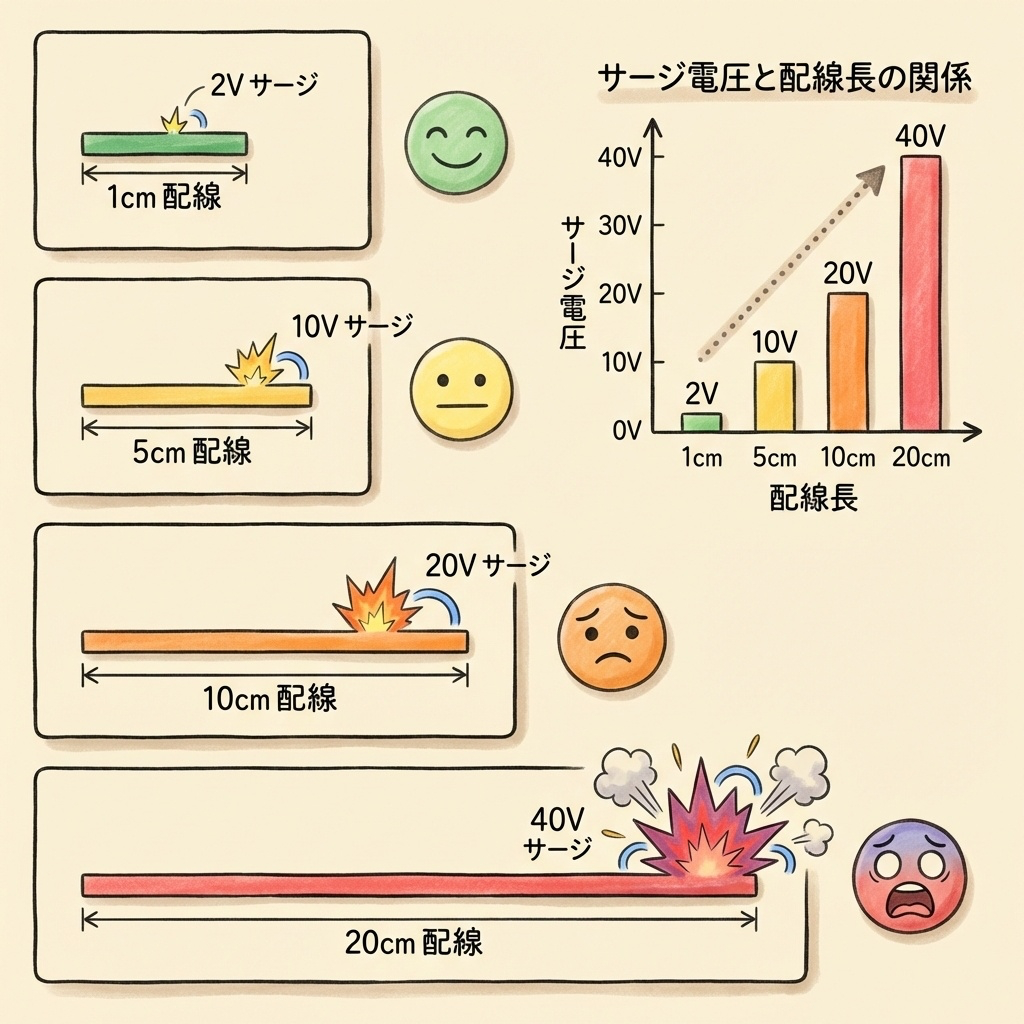

計算例①:基板パターン長さの影響

| スイッチング電流 I | 10 A |

| スイッチング時間(ターンオフ) | 50 ns |

| パターンのインダクタンス | 10 nH/cm |

まず、dI/dt を計算します:

【dI/dt の計算】

dI/dt = ΔI / Δt = 10A / 50ns

dI/dt = 10 / (50 × 10⁻⁹)

dI/dt = 2 × 10⁸ A/s = 200 A/μs

次に、パターン長さを変えてサージ電圧を計算します:

| パターン長さ | インダクタンス L | サージ電圧 V |

|---|---|---|

| 1 cm | 10 nH | 2 V |

| 5 cm | 50 nH | 10 V |

| 10 cm | 100 nH | 20 V |

| 20 cm | 200 nH | 40 V ! |

たった20cmの配線が、40Vものサージ電圧を生み出します。これが電源電圧に上乗せされるため、例えば48V電源なら素子には最大88Vがかかることになります。耐圧100Vのデバイスでもギリギリです。

計算例②:スイッチング速度の影響

同じ条件で、スイッチング時間を変えた場合を見てみましょう(L = 50nH固定)。

| スイッチング時間 | dI/dt | サージ電圧 V |

|---|---|---|

| 10 ns(超高速) | 1000 A/μs | 50 V ! |

| 50 ns(高速) | 200 A/μs | 10 V |

| 200 ns(中速) | 50 A/μs | 2.5 V |

GaNやSiCなどの次世代デバイスは、10ns以下の超高速スイッチングが可能です。これによりスイッチング損失は減少しますが、dI/dtが大きくなるためサージ電圧は増加します。高速デバイスほど、配線インダクタンスの低減が重要になります。

配線インダクタンスを減らす設計テクニック

サージを根本から減らすには、配線インダクタンスLを小さくすることが最も効果的です。具体的なテクニックを見ていきましょう。

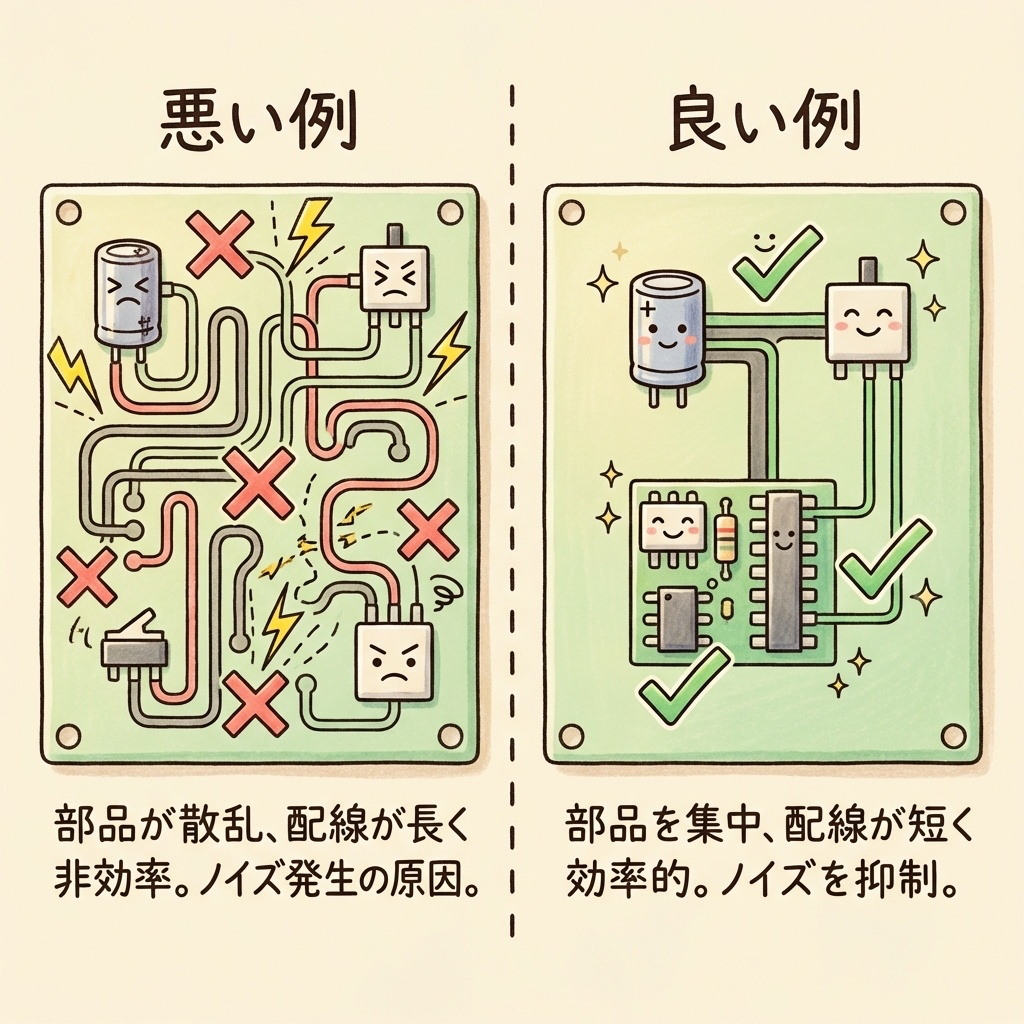

テクニック①:配線を短くする

最もシンプルで効果的な方法です。配線が短いほどインダクタンスは小さくなります。

悪い例

- パワー部品が基板の端に分散

- 主回路ループが大きい

- コンデンサがスイッチから遠い

良い例

- パワー部品を集中配置

- 主回路ループが最小

- コンデンサはスイッチの直近に

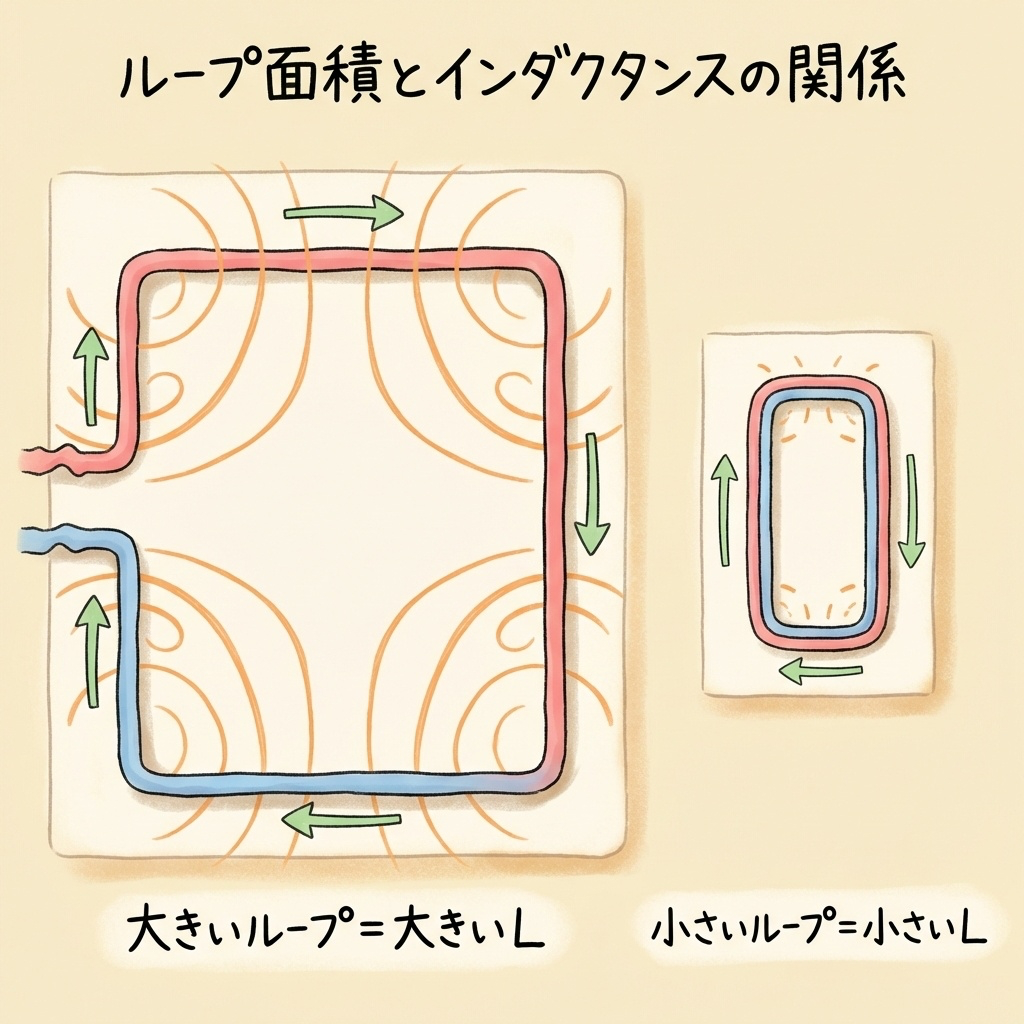

テクニック②:ループ面積を小さくする

配線のインダクタンスは、単に「長さ」だけでなく「ループ面積」にも大きく依存します。往路と復路が離れているほど、インダクタンスは大きくなります。

ループインダクタンスは、ループの面積に比例します。

L ≈ μ₀ × (ループ面積) / (ループの長さ)

→ループ面積を半分にすれば、インダクタンスも約半分に!

大きいループ

往路と復路が離れている

→ループ面積大

→インダクタンス大

→サージ大!

小さいループ

往路と復路が隣接・重なる

→ループ面積小

→インダクタンス小

→サージ小!

テクニック③:電源-GNDの層を隣接させる

多層基板では、電源層とGND層を隣接した層に配置することで、ループインダクタンスを大幅に低減できます。

📐 層構成の例(4層基板)

| L1:信号層(TOP) |

| L2:GND層 ← 隣接! |

| L3:電源層 ← 隣接! |

| L4:信号層(BOTTOM) |

L2とL3が隣接しているため、電源-GND間のインダクタンスが最小化されます。

テクニック④:デカップリングコンデンサを近くに配置

デカップリングコンデンサ(バイパスコンデンサ)は、スイッチング素子のできるだけ近くに配置します。コンデンサとスイッチの間の配線が長いと、その分のインダクタンスがサージの原因になります。

「コンデンサを入れたのにサージが減らない」という場合、コンデンサの配置が遠すぎることが原因であることが多いです。コンデンサ自体の特性よりも、配線インダクタンスのほうが支配的になっている可能性があります。

dI/dt を抑える方法(トレードオフあり)

サージを減らすもう一つの方法は、dI/dt(電流変化率)を小さくすることです。ただし、これには重要なトレードオフがあります。

ゲート抵抗でスイッチング速度を調整

MOSFETやIGBTのゲートに入れるゲート抵抗(Rg)の値を大きくすると、スイッチング速度が遅くなり、dI/dtが小さくなります。

小さいRg(高速スイッチング)

- ✅ スイッチング損失が小さい

- ❌ dI/dtが大きい → サージ大

- ❌ EMIノイズが大きい

大きいRg(低速スイッチング)

- ✅ dI/dtが小さい → サージ小

- ✅ EMIノイズが小さい

- ❌ スイッチング損失が大きい

最適なバランスを見つける

実際の設計では、サージと損失のバランスを見ながらゲート抵抗を調整します。

まずは配線インダクタンスを最小化(これが最優先)

それでもサージが大きければ、ゲート抵抗を大きくしてdI/dtを抑制

損失が許容範囲を超えるなら、スナバ回路を追加

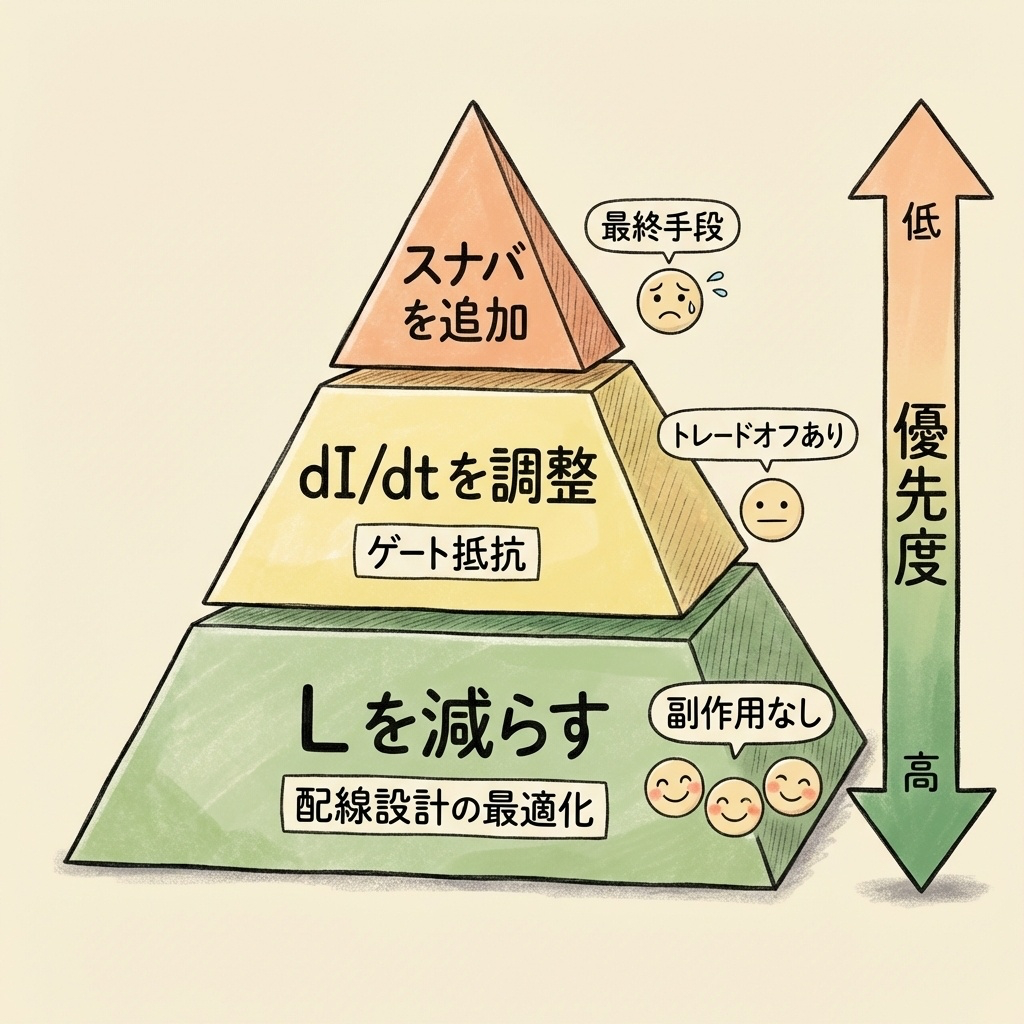

サージ対策の優先順位は以下の通りです:

1. Lを減らす(配線設計の最適化)← 最も効果的、副作用なし

2. dI/dtを調整(ゲート抵抗の調整)← 効果あり、損失とのトレードオフ

3. スナバを追加(RC、RCD、アクティブクランプ)← 最終手段

実務で使える設計チェックリスト

配線インダクタンスを最小化するための、実務で使えるチェックリストをまとめました。

✅ 配線インダクタンス低減チェックリスト

【部品配置】

- □ パワー部品(スイッチ、ダイオード、コンデンサ)を集中配置している

- □ デカップリングコンデンサはスイッチの直近(5mm以内が理想)

- □ 主回路のループ面積が最小になる配置になっている

【パターン設計】

- □ 電源パターンとGNDパターンが隣接・並走している

- □ 大電流パターンは太く・短く設計している

- □ ビアを多用して層間接続のインダクタンスを低減している

【層構成(多層基板)】

- □ 電源層とGND層が隣接した層に配置されている

- □ 高速スイッチングのリターンパスが確保されている

【その他】

- □ リード線やジャンパー線を極力使用していない

- □ 表面実装部品を優先的に使用している

まとめ

配線インダクタンスとサージ電圧の関係について解説しました。

📌 この記事のポイント

- V = L × dI/dt:サージ電圧を決める最も重要な式

- インダクタンスL:配線の長さとループ面積に比例

- dI/dt:スイッチングが速いほど大きくなる

- サージを減らす優先順位:①Lを減らす → ②dI/dtを調整 → ③スナバ追加

- 配線設計:パワー部品を集中配置、ループ面積を最小化

この式を理解すれば、サージの発生原因も、対策の方向性もすべてわかります。

スナバ回路は「発生したサージを処理する」手段ですが、本当に重要なのは「サージを発生させない」設計です。配線インダクタンスを最小化することで、スナバ回路の負担を減らし、より高効率で信頼性の高い回路を実現できます。

📚 次に読むべき記事

具体的なパターン設計テクニックを学ぶ

配線最適化後もサージが残る場合のスナバ設計

多層基板でインダクタンスを低減する方法

サージ対策を体系的に学びたい方は、以下の順番で読むのがおすすめです:

- 配線インダクタンスとサージの関係(この記事) ← 根本原因を理解

- スナバ回路とは?(基礎)

- RCスナバ回路の設計計算

- RCDスナバ回路の設計

- アクティブクランプ回路

- TVSダイオードの選び方

💡 設計の心得

「スナバ回路を入れればサージは解決する」と考えがちですが、それは「治療」に過ぎません。本当に優れた設計は、「予防」としてサージを発生させないことです。

V = L × dI/dt の式を常に意識し、配線インダクタンスを最小化する設計を心がけてください。スナバ回路は、それでも残るサージに対する「最後の砦」として使いましょう。