- 「スイッチング電源がノイズを出すのは知っているけど、"なぜ"かは説明できない」

- 「V=L×dI/dtの式は見たことあるけど、直感的にピンとこない」

- 「dI/dtとdV/dtって何が違うの?どっちがどのノイズの原因?」

- 「スイッチング周波数を上げると小型化できるのに、なぜノイズが増えるの?」

- スイッチング動作が「本質的にノイズを生む」物理的な理由

- V=L×dI/dtの意味を「水道管のウォーターハンマー」で直感的に理解

- dI/dtが伝導ノイズ、dV/dtが放射ノイズの主犯である仕組み

- スイッチング周波数が高いほどノイズが増える「トレードオフの正体」

スイッチング電源は、現代の電子機器にとって不可欠な存在です。スマートフォンの充電器、ノートPCのACアダプタ、産業用機器の電源ユニット――あらゆる場所で使われています。

でも、スイッチング電源には宿命的な弱点があります。それは「ノイズの塊」であること。

「ノイズが出る」ということは何となく知っていても、「なぜ出るのか?」「物理的に何が起きているのか?」を明確に説明できる人は意外と少ないのではないでしょうか。

この記事では、スイッチング電源がノイズを発生させるメカニズムを、たった2つの式(V=L×dI/dtとI=C×dV/dt)で完全に理解できるよう、たとえ話と図解で徹底的に解説します。

目次

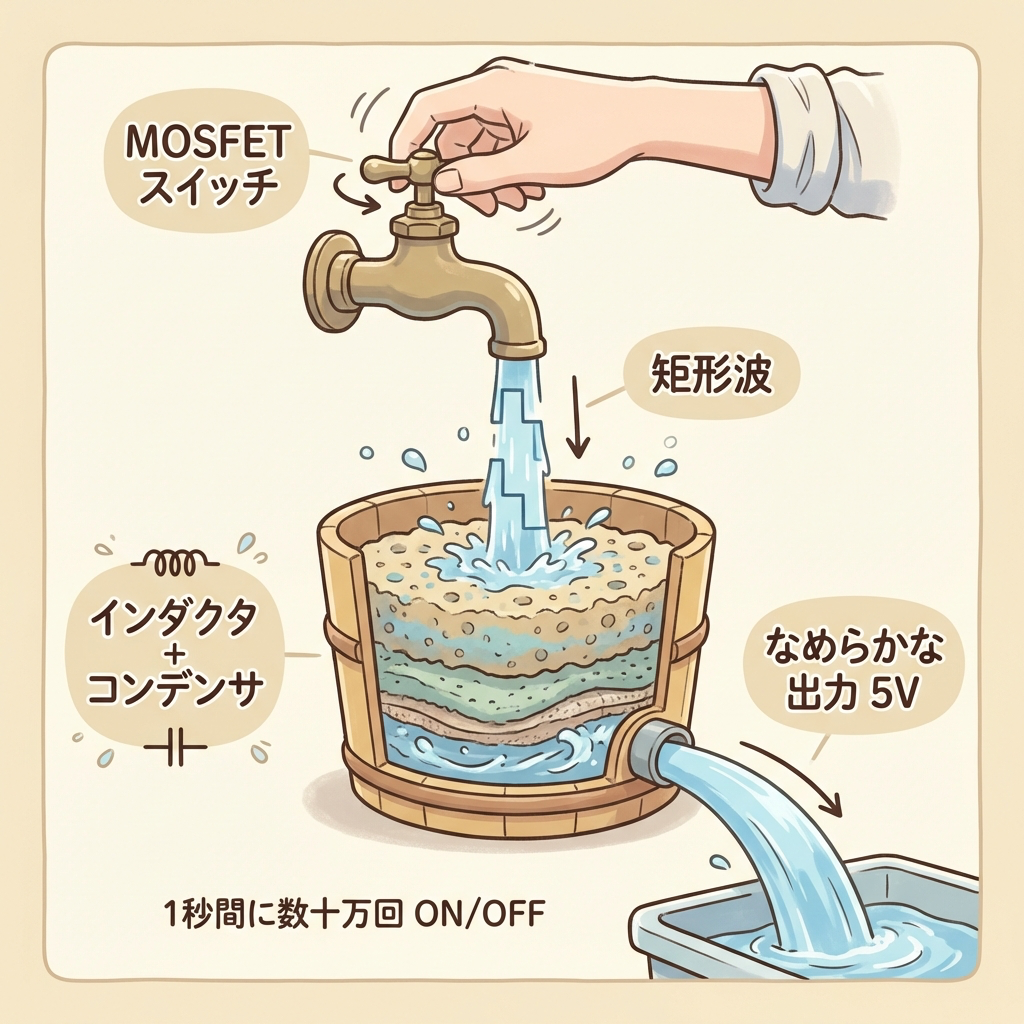

前提知識|スイッチング電源は「蛇口を高速でON/OFFする」装置

💡 スイッチング電源の動作原理を30秒で理解

スイッチング電源を一言で説明するなら、「電気の蛇口を1秒間に数十万回〜数百万回開け閉めして、欲しい電圧を作る装置」です。

たとえば、12Vの入力から5Vの出力を作りたい場合。スイッチ(MOSFET)で12Vを高速にON/OFFし、ON時間の割合(デューティ比)を約42%にすると、平均電圧がちょうど5Vになります。これをインダクタとコンデンサで平滑化して、なめらかな5Vの直流を取り出すわけです。

この「高速ON/OFF」のおかげで効率90%以上を実現できるのですが、まさにこの「ON/OFF」こそがノイズの根源なのです。

🆚 リニア電源はなぜ静かなのか?

スイッチング電源の対極にあるのが「リニア電源(シリーズレギュレータ)」です。リニア電源は、トランジスタを「可変抵抗」として使い、余分な電圧を熱として捨てる方式です。

リニア電源ではスイッチングが起きないため、急激な電流・電圧の変化が発生しません。だからノイズがほとんど出ない。しかしその代わり、効率が悪く(40~60%程度)、発熱が大きいというデメリットがあります。

リニア電源

- スイッチングなし → ノイズが極小

- 効率 40~60%(余分は熱に)

- サイズが大きい

- 用途:オーディオ、計測器など

スイッチング電源

- 高速ON/OFF → ノイズが大

- 効率 85~95%

- 小型・軽量

- 用途:ほぼすべての電子機器

スイッチング電源のノイズは「設計が悪いから出る」のではありません。電流をON/OFFするという動作原理そのものが、物理的にノイズを生むのです。つまり「ノイズゼロのスイッチング電源」は原理的に存在しません。できるのは「ノイズを規格値以下に抑える」ことだけです。

ノイズの主犯①:dI/dt|「電流の急変」が電圧スパイクを生む

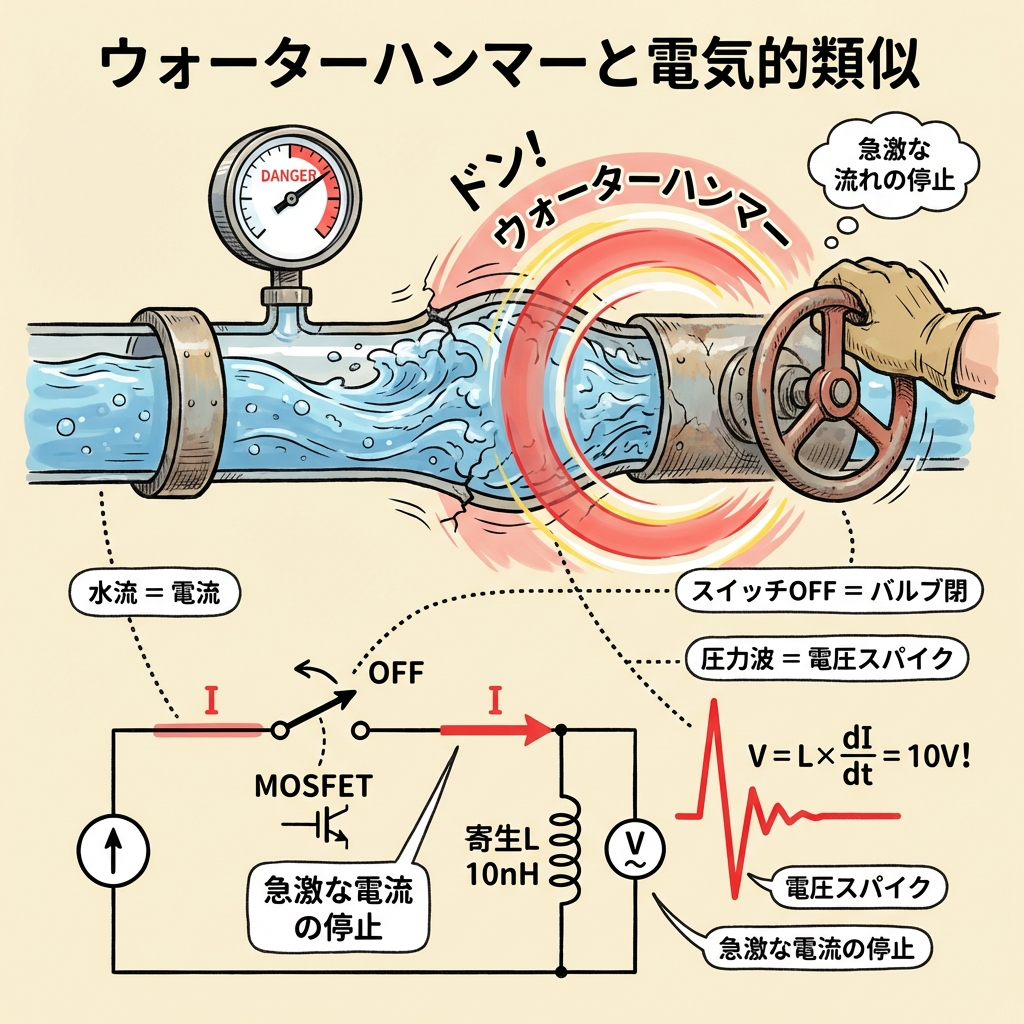

🚰 V=L×dI/dtを「水道管」で理解する

スイッチング電源のノイズを理解する上で、最も重要な式がこれです。

L:配線や部品が持つインダクタンス(寄生インダクタンス)

dI/dt:電流の変化速度(1秒あたり何アンペア変化するか)

この式を水道管でたとえましょう。

水道管(=配線)を水(=電流)が勢いよく流れているとします。ここで蛇口(=スイッチ)を一瞬で閉めると、何が起きるでしょうか?

「ドン!」という衝撃が水道管全体に走りますよね。これがいわゆる「ウォーターハンマー(水撃)」です。流れていた水が急に止められると、運動エネルギーが行き場を失い、水道管の壁に大きな圧力(=電圧スパイク)がかかるのです。

蛇口を一瞬で閉める(dI/dtが大きい)→ 水の勢いが止まれず管が「ドン!」と振動(電圧スパイク発生)→ 振動が管全体に伝播(ノイズが放射・伝導)

MOSFETが一瞬でOFF(dI/dtが大きい)→ 電流が止まれず配線のインダクタンス(L)にエネルギーが蓄積→ V=L×dI/dtの電圧スパイクが発生→ スパイクが配線を伝わってノイズになる

📊 具体的な数値で実感する|たった1cmの配線で10Vのノイズ

「配線のインダクタンスなんて微々たるものでしょ?」と思うかもしれません。実際に計算してみましょう。

条件

・配線のインダクタンス L = 10nH(基板上の約1cmの配線に相当)

・スイッチング時の電流変化 ΔI = 5A

・スイッチング時間 Δt = 5ns(高速MOSFETの典型値)

計算

たった1cmの配線が、10Vもの電圧スパイクを生むのです。

この10Vのスパイクは、回路図にも基板図面にも描かれていない「見えない電圧」です。これが電源ラインに乗って外部に流れ出れば伝導ノイズに、配線がアンテナとして放射すれば放射ノイズになります。

式の中の「L」は、コイルやインダクタのことではありません。基板の配線パターン、ビア、部品のリード線など、あらゆる導体が持つ微小なインダクタンス(=寄生インダクタンス)です。回路図には載っていませんが、物理的に必ず存在します。だから「回路図通りに作ったのにノイズが出る」のです。

ノイズの主犯②:dV/dt|「電圧の急変」が浮遊容量を通じてノイズを撒き散らす

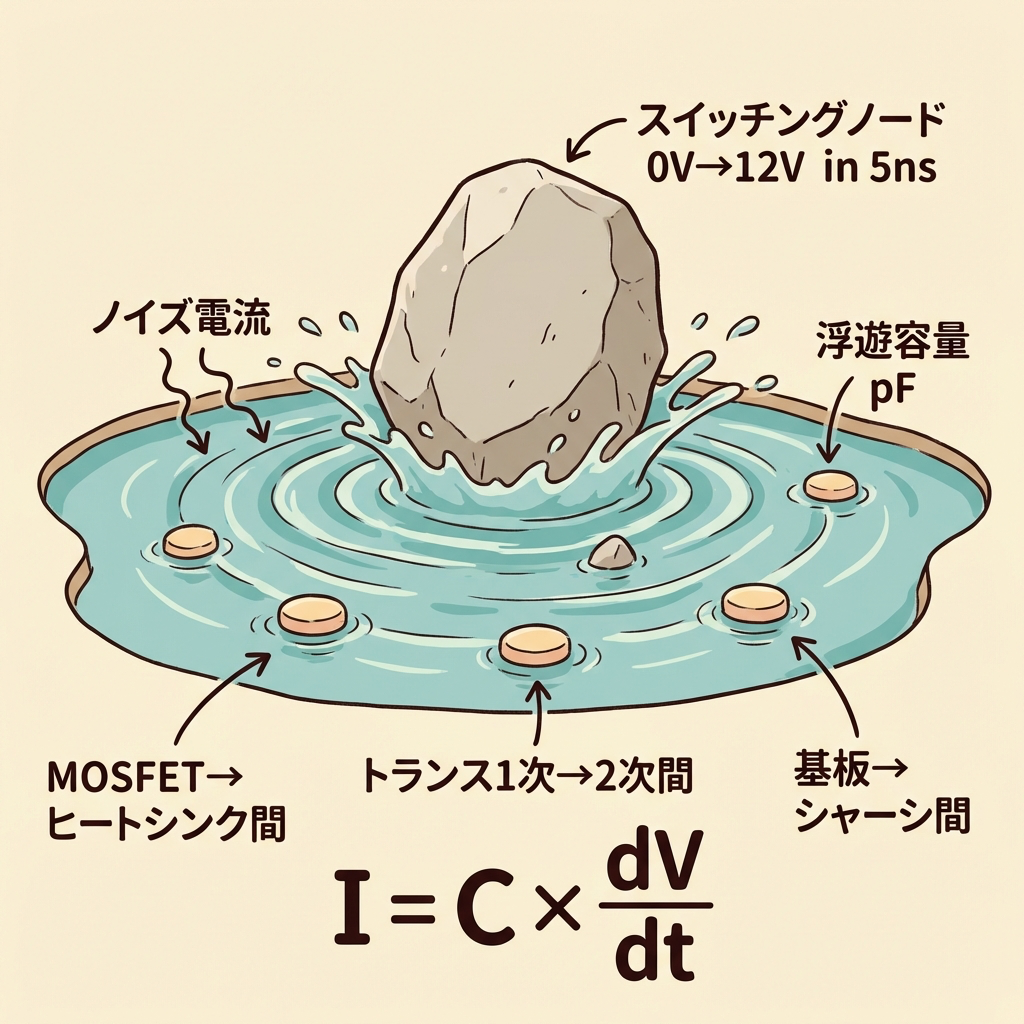

⚡ I=C×dV/dtを「水面の波紋」で理解する

dI/dtが「電流の急変」によるノイズの主犯だとすると、もうひとりの主犯がdV/dtです。

C:浮遊容量(導体間、基板とシャーシ間の微小なコンデンサ)

dV/dt:電圧の変化速度(1秒あたり何ボルト変化するか)

池に石を「ポチャン」と投げると、水面に波紋が広がりますよね。ゆっくり石を沈めれば波紋はほとんど立ちません。でも、石を思い切り叩きつけると、大きな波紋が遠くまで広がります。

スイッチング電源の「スイッチングノード」と呼ばれるポイントでは、電圧が0V→12Vに数ナノ秒で急変します。このdV/dtが非常に大きいため、回路の至るところにある浮遊容量(意図しない微小なコンデンサ)を通じて、ノイズ電流が流れ出します。

🔍 浮遊容量はどこにある?

「コンデンサなんて付けてないのに?」と思うかもしれません。しかし、浮遊容量は設計者が意図しなくても物理的に存在します。

| 浮遊容量の場所 | 典型的な値 | なぜ問題? |

|---|---|---|

| MOSFETのドレイン→ヒートシンク間 | 10~100pF | ヒートシンクが「アンテナ」になる |

| トランスの1次巻線→2次巻線間 | 10~50pF | 絶縁を飛び越えてノイズが2次側へ |

| 基板パターン→シャーシ(GND)間 | 数pF~数十pF | シャーシ経由で外部にノイズが漏洩 |

これらの浮遊容量を通じてノイズ電流が流れ出す現象は、「コモンモードノイズ」の主因です。コモンモードノイズはEMC試験で最も厄介な存在であり、多くの設計者を苦しめています。

dI/dt(電流の急変)→ 配線のインダクタンスに電圧スパイクを発生させ、主にノーマルモードの伝導ノイズの原因になる

dV/dt(電圧の急変)→ 浮遊容量を通じてノイズ電流を流し出し、主にコモンモードの放射ノイズの原因になる

つまり、スイッチング動作の「ON/OFF」の瞬間に、dI/dtとdV/dtの両方が同時に発生し、2種類のノイズを撒き散らしているのです。

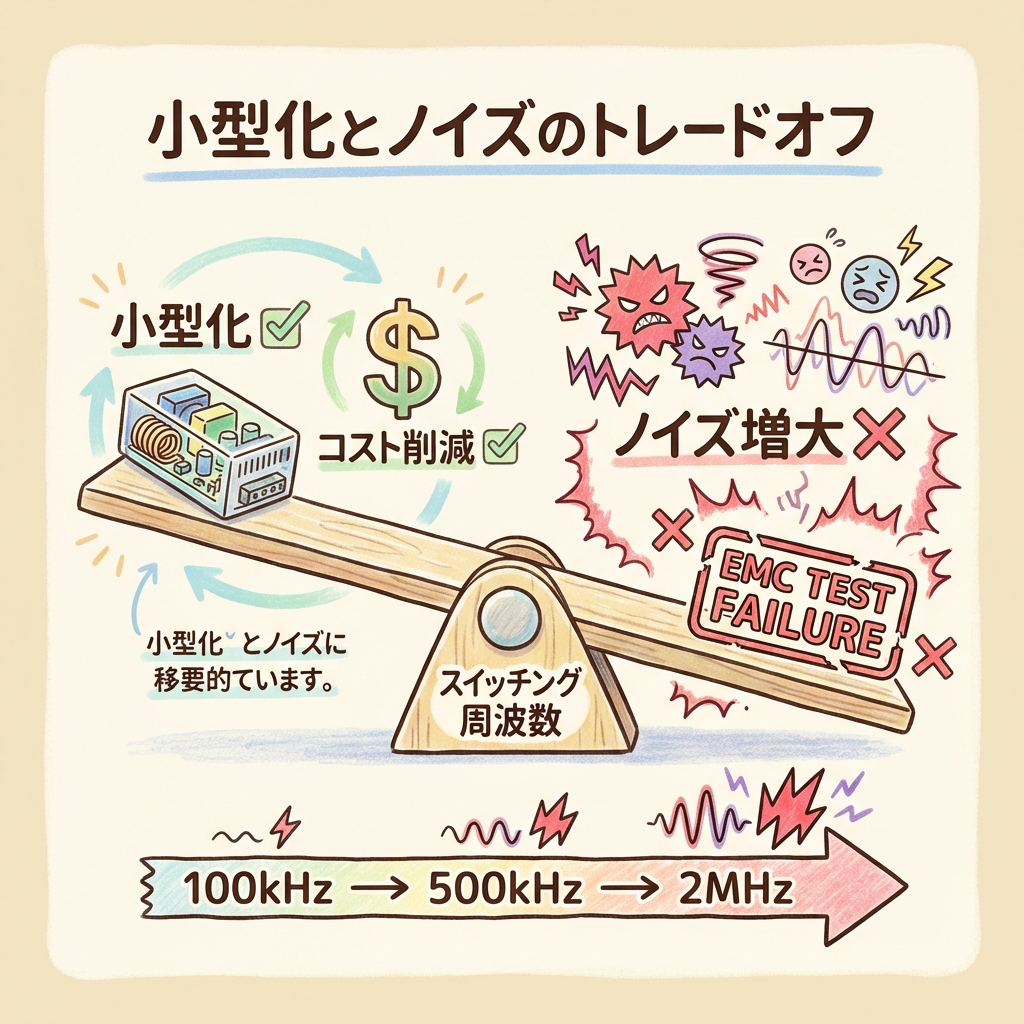

スイッチング周波数が高いほどノイズが増える理由

📈 「小型化の代償」というトレードオフ

スイッチング電源の設計では、「スイッチング周波数を上げると、インダクタやコンデンサを小さくできる=電源が小型化できる」という大きなメリットがあります。

しかし、周波数を上げるということは、「1秒あたりのON/OFFの回数が増える」ということです。

これを先ほどの水道管のたとえに戻すと、蛇口を1秒に10万回叩きつけていたのを、100万回叩きつけるようにするようなもの。当然、「ドン!」という衝撃(ノイズ)の頻度が増え、ノイズのエネルギーの総量が増大します。

🎵 高調波が広い周波数帯域に拡散する

もうひとつ重要なのは、スイッチング波形(矩形波)は「基本周波数」だけでなく、その整数倍の高調波を含んでいるということです。

たとえば、スイッチング周波数が500kHz(0.5MHz)の場合、ノイズは0.5MHz、1MHz、1.5MHz、2MHz……と高調波として広がっていきます。理論的には無限に続きますが、実際にはスイッチングのエッジ(立ち上がり/立ち下がり)の速度で決まる「折れ点周波数」の上方でノイズは減衰していきます。

| スイッチング周波数 | ノイズが届く周波数帯 | 影響 |

|---|---|---|

| 100kHz | ~数十MHz | 主に伝導ノイズ |

| 500kHz | ~100MHz以上 | 伝導+放射ノイズ |

| 2MHz以上 | ~数百MHz〜GHz帯 | ⚠️ 放射ノイズが深刻化。EMC試験で問題になりやすい |

近年主流になりつつあるGaN(窒化ガリウム)やSiC(炭化ケイ素)のパワーデバイスは、従来のSi MOSFETよりもはるかに高速にスイッチングできます(立ち上がり時間 1~5ns)。これは効率向上・小型化に有利ですが、dI/dtとdV/dtがさらに大きくなるため、ノイズ対策の難易度も格段に上がっているのが現状です。

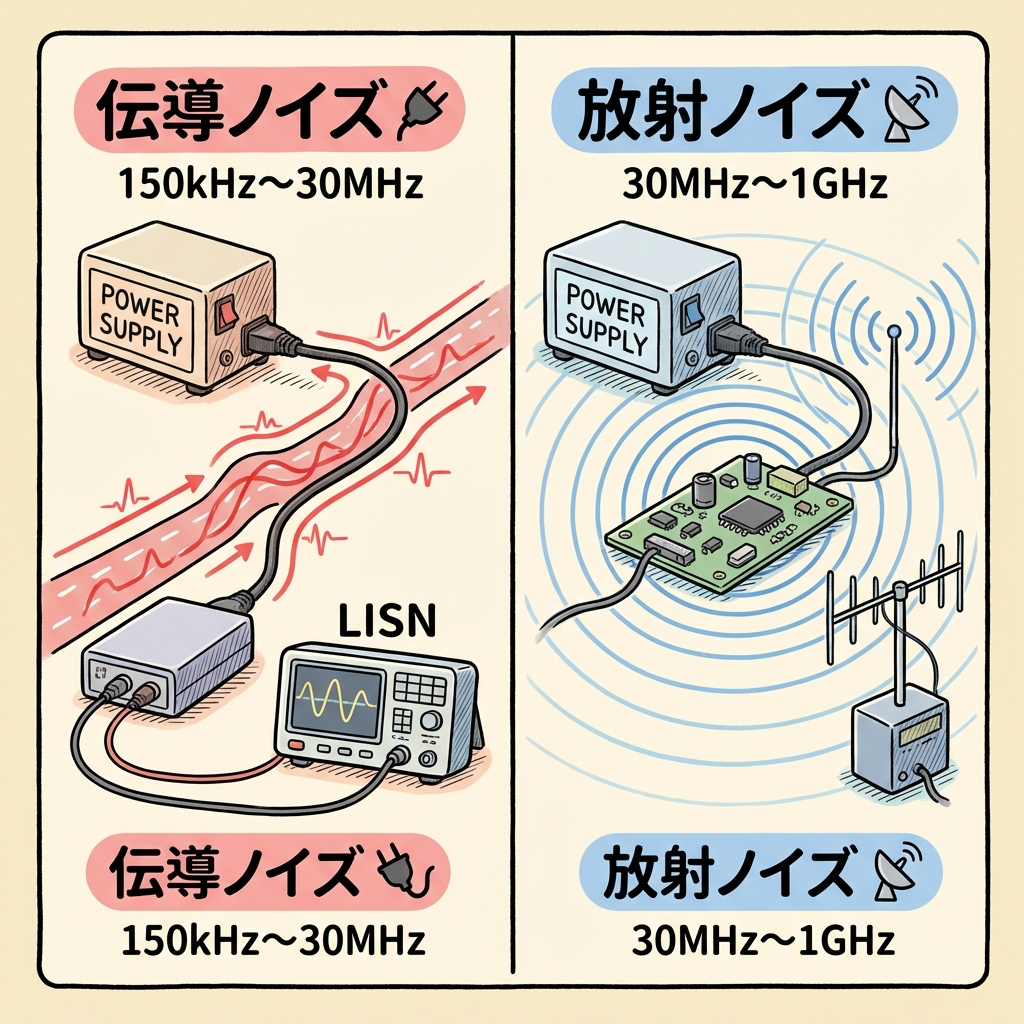

ノイズはどこから外に出ていくのか?|2つの経路

🔌 経路①:伝導ノイズ|電源ケーブルを「高速道路」にして外へ

スイッチング動作で発生した高周波のノイズ電流は、電源の入力ケーブル(ACコードやDC入力線)を伝わって外部に流れ出します。これが伝導ノイズです。

たとえるなら、工場の排水が下水道を通じて川に流れ出るイメージです。工場内でいくら浄化しても、排水口が開いていれば汚染水は外へ出ていきます。伝導ノイズの「排水口」は電源ケーブルです。EMC規格では、150kHz~30MHzの周波数帯で伝導ノイズの限度値を定めています。

📡 経路②:放射ノイズ|基板やケーブルが「アンテナ」になって電波を飛ばす

もうひとつの経路が放射ノイズです。基板上のパターン、外部接続ケーブル、筐体の隙間などが「意図しないアンテナ」として機能し、ノイズを電磁波として空中に放射します。

特にスイッチングノード(MOSFETのドレインなど)は、電圧が0V→数十Vの間で数ナノ秒で変動する「超高速の振動板」です。この振動が浮遊容量を経由してシャーシやヒートシンクに伝わり、大きな金属面がアンテナとして電波を飛ばします。EMC規格では、30MHz~1GHzの周波数帯で放射ノイズの限度値を定めています。

伝導ノイズ

- 経路:電源ケーブルを伝わる

- 主犯:dI/dt(電流の急変)

- 規制帯域:150kHz~30MHz

- 対策:EMIフィルタ、パスコン、ループ面積縮小

放射ノイズ

- 経路:基板・ケーブルから空中に放射

- 主犯:dV/dt(電圧の急変)+ 浮遊容量

- 規制帯域:30MHz~1GHz

- 対策:シールド、GNDプレーン、スナバ回路

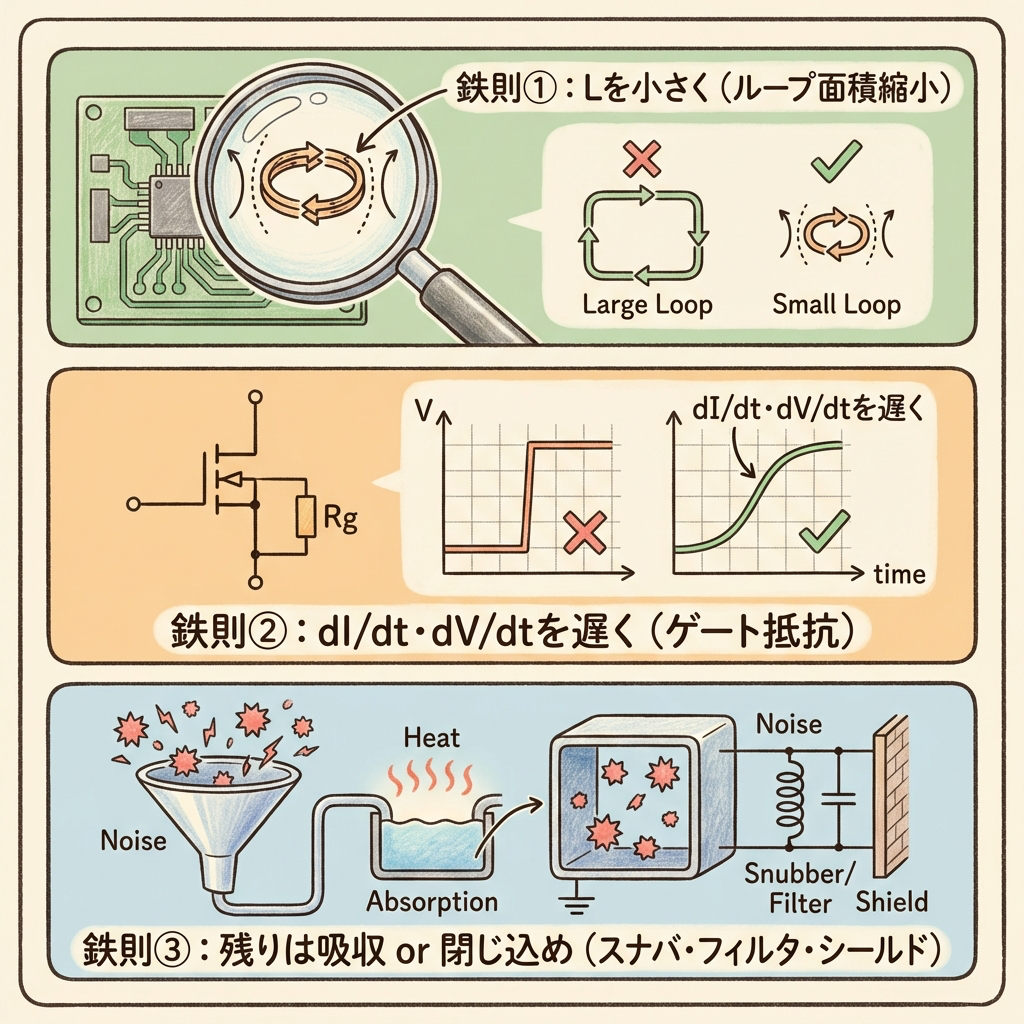

ノイズを減らすための「3つの鉄則」

ここまでの内容を踏まえると、スイッチング電源のノイズを減らすための戦略は、V=L×dI/dtとI=C×dV/dtの式から逆算できます。

🔧 鉄則①:L(寄生インダクタンス)を小さくする

V=L×dI/dtの「L」を小さくすれば、同じdI/dtでも発生する電圧スパイクが小さくなります。具体的には、電流ループ面積を最小化することです。

スイッチング電流が流れるループ(MOSFETのドレイン→インダクタ→出力コンデンサ→GND→入力コンデンサ→MOSFETのソース)の面積を小さくするほど、配線のインダクタンスが減り、ノイズが減ります。部品配置の段階で「パワーループの面積」を最小にすることが、最も効果的なEMC対策です。

🔧 鉄則②:dI/dtとdV/dtを遅くする(スイッチング速度を下げる)

蛇口をゆっくり閉めればウォーターハンマーが減るように、MOSFETのスイッチング速度を遅くすれば、dI/dtとdV/dtが小さくなりノイズが減ります。

具体的な手段としては、ゲート抵抗を大きくする(ゲートの充放電を遅くしてON/OFFの速度を落とす)方法があります。ただし、スイッチング速度を下げるとターンオン/ターンオフ時の損失(スイッチング損失)が増えるため、ノイズと効率のトレードオフになります。

🔧 鉄則③:発生したノイズを「吸収」または「閉じ込める」

鉄則①②で対策しても、ノイズをゼロにすることはできません。残ったノイズは「吸収」か「閉じ込め」で対処します。

| 対策手法 | 役割 | 対象 |

|---|---|---|

| スナバ回路 | 電圧スパイクを吸収 | スイッチングノードのリンギング |

| EMIフィルタ | 電源ラインのノイズを遮断 | 伝導ノイズ |

| シールド(金属筐体) | 電磁波を閉じ込める | 放射ノイズ |

| フェライトビーズ | 高周波ノイズを熱に変換して吸収 | 電源ライン・信号ラインの高周波ノイズ |

ノイズ対策で最も効果的なのは「発生源で抑える(鉄則①②)」こと。フィルタやシールドは「発生した後に対処する」手段なので、コストも手間も多くなります。設計の初期段階でループ面積とスイッチング速度を最適化することが、最もコストパフォーマンスの高い対策です。

まとめ|すべてのノイズは「急」がつく変化から生まれる

この記事の内容を振り返りましょう。

| なぜノイズが出る? | スイッチング電源は電流を高速でON/OFFする装置。この「急激な変化」が物理的にノイズを生む |

| dI/dtの役割 | V=L×dI/dt:電流の急変が、配線の寄生インダクタンスに電圧スパイクを発生させる。主に伝導ノイズの原因 |

| dV/dtの役割 | I=C×dV/dt:電圧の急変が、浮遊容量を通じてノイズ電流を流し出す。主に放射ノイズ(コモンモード)の原因 |

| 周波数が高いと? | ON/OFFの回数が増え、高調波が広い周波数帯に拡散するためノイズが増大 |

| 3つの鉄則 | ①L(ループ面積)を小さく ②dI/dt・dV/dtを遅く ③残りは吸収 or 閉じ込め |

スイッチング電源のノイズは、「設計が悪い」から出るのではなく、「電流をON/OFFするという動作原理そのもの」から物理的に生まれるものです。

この「なぜ」を理解していると、ノイズ対策が「おまじない」ではなく「物理的に筋の通った行為」として見えるようになります。GNDプレーンを広げる理由も、スナバ回路を入れる理由も、すべてはV=L×dI/dtとI=C×dV/dtの式に帰着するのです。

📚 次に読むべき記事

本記事の基礎編。ループ面積とdI/dtの関係を、より実践的な基板配置の視点から解説しています。

dV/dtが生むコモンモードノイズの正体を深掘り。EMC試験で最も厄介なノイズの仕組みを理解できます。

ノイズが外に出る2つの経路を、測定方法の違いも含めて解説しています。

鉄則③「発生したノイズを吸収する」の代表的な手段であるスナバ回路の解説です。

ループ面積を小さくするには、GNDの「帰り道」を理解することが不可欠です。

高周波電流が実際にどこを流れるのか。GNDプレーンの重要性が体感できる記事です。

パスコン(バイパスコンデンサ)が電源ノイズを吸収する物理的な仕組みを解説しています。

パワー系とデジタル系のGNDをどう分離するか。実践的なGND設計の全手順です。

鉄則①の実践編。ハイサイド・ローサイド・入力コンデンサの配置ルールを具体的に解説しています。

V=L×dI/dtの式をさらに深掘り。配線インダクタンスの推定方法とサージ電圧の計算例を解説しています。

MOSFETの選定がdI/dtとdV/dtに直結します。スイッチング速度と損失のトレードオフを理解する記事です。

鉄則②のスイッチング速度制御に直結するゲート駆動回路の設計ガイドです。

スイッチング電源の周辺回路をまとめて俯瞰したい方はこちらから。