- 「LDOとスイッチングレギュレータ、どっちを使えばいいの?」と設計のたびに悩む

- 「効率が高い=正義」と思って全部スイッチングにしたらノイズで痛い目にあった

- 「LDOは損失が大きい」と聞いたけど、どんな場面なら使っていいのかわからない

- 先輩に「ここはLDOでいいよ」と言われたけど、"なぜ"が理解できなかった

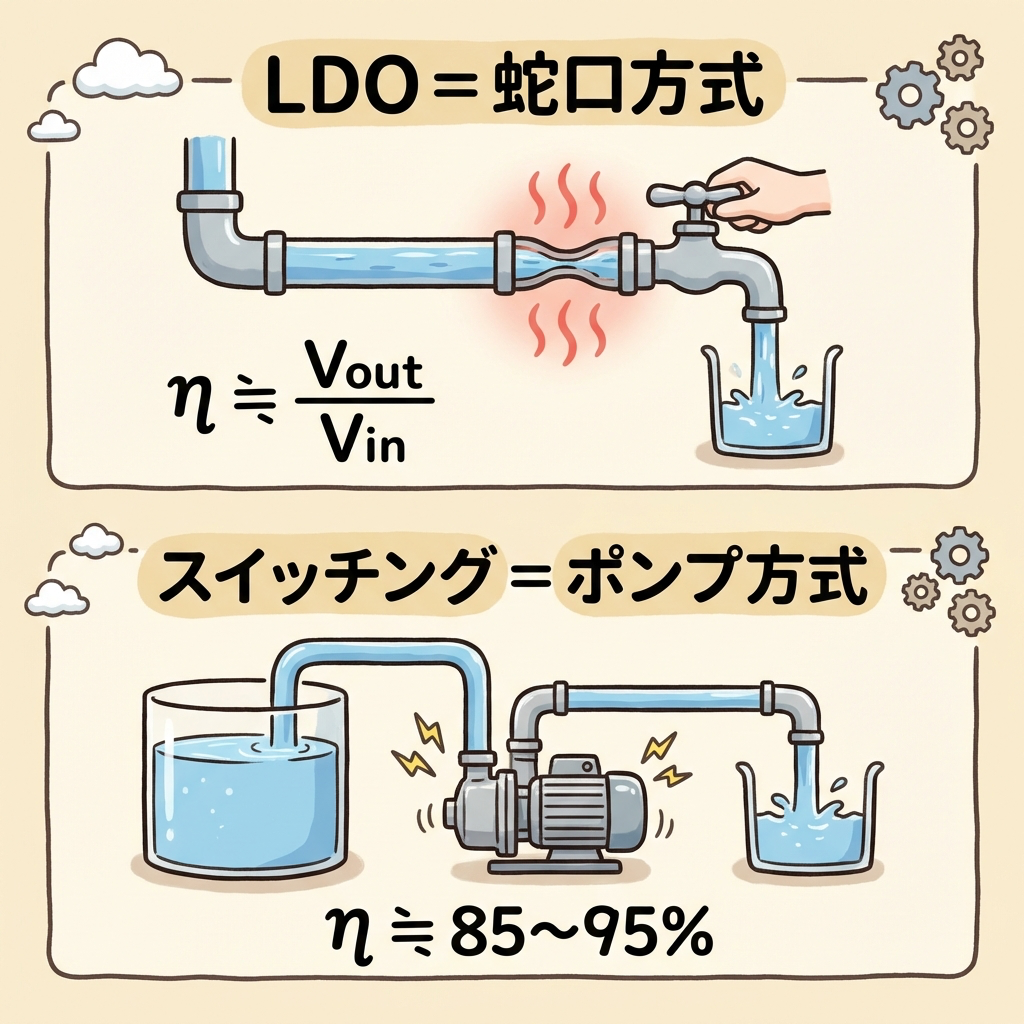

- LDOとスイッチングレギュレータの動作原理の違いを「蛇口」と「ポンプ」で直感理解

- 効率・ノイズ・コスト・サイズ・発熱の5つの判断軸を数値で比較

- 「どっちを選ぶ?」が一発でわかるフローチャート

- プロが実務で使う「スイッチング+後段LDO」のハイブリッド構成

電源回路を設計するとき、「LDOにするか、スイッチングレギュレータにするか」は避けて通れない選択です。

「効率が高いほうがいいに決まってる」と思ってスイッチングレギュレータを選んだら、ADCの精度がガタガタになった……。逆に「LDOなら安心」と思って使ったら、ICが触れないほど熱くなった……。こんな失敗、実は設計の現場では日常茶飯事です。

この記事では、LDOとスイッチングレギュレータの「本質的な違い」を、水道の蛇口やポンプに例えて中学生でもわかるように解説します。読み終わるころには、「この条件ならLDO」「この条件ならスイッチング」と自信を持って判断できるようになっているはずです。

【完全図解】パワエレに必要な周辺回路まとめ|スナバ回路・ゲート駆動・保護回路を「なぜ必要か」から徹底解説 →

目次

そもそもLDOとスイッチングレギュレータは「何が違う」のか?

まずは2つの電源ICの動作原理の違いを、誰でもイメージできる「たとえ話」で掴みましょう。

🚰 LDO=「蛇口を絞って水量を調整する」方式

LDO(Low Dropout Regulator)は、リニアレギュレータの一種です。動作原理はとてもシンプルで、「高い電圧をわざと抵抗で落として、低い電圧を作る」という方法です。

水道で例えると、蛇口を絞って水の勢いを調整するのと同じ。蛇口を絞る=エネルギーを捨てている、ということです。捨てたエネルギーは熱になります。

η ≒ VOUT / VIN

※自己消費電流を無視した簡易式。入力と出力の電圧差が大きいほど効率が下がる。

例えば、5V→3.3Vに降圧する場合、効率は3.3÷5=66%。残りの34%は全部「熱」として捨てていることになります。5V→1.0Vなら効率はたったの20%。これがLDOの最大の弱点です。

⚡ スイッチングレギュレータ=「ポンプで水を汲み上げて必要な量だけ送る」方式

スイッチングレギュレータは、スイッチ素子(MOSFETなど)を高速でON/OFFして、インダクタ(コイル)とコンデンサにエネルギーを蓄え、必要な電圧に変換する方式です。

水道で例えると、ポンプを使って「必要な分だけ」水を送るイメージ。蛇口のようにエネルギーを「捨てる」のではなく、「変換する」ので効率が高い。典型的な効率は85〜95%にもなります。

ただし、ポンプはガタガタと振動(=スイッチングノイズ)を出します。これがスイッチングレギュレータの弱点です。

LDO(リニア方式)

- 蛇口を絞って電圧を落とす

- 余った電圧は熱になる

- 構造がシンプル

- スイッチングしないのでノイズが少ない

- 効率 ≒ VOUT / VIN

スイッチングレギュレータ

- ON/OFFを繰り返して電圧を変換する

- エネルギーを「変換」するので高効率

- インダクタ・コンデンサが必要で回路が複雑

- スイッチングによりノイズ・EMIが発生

- 効率 ≒ 85〜95%(降圧比に大きく依存しない)

LDOは「エネルギーを捨てて電圧を下げる」、スイッチングレギュレータは「エネルギーを変換して電圧を変える」。この違いさえ覚えておけば、すべての特性差を理解する土台になります。

LDO vs スイッチングレギュレータ|5つの判断軸で徹底比較

「どっちを使うか」を判断するために、設計者が実際に見ている5つの軸を一覧表で整理しました。

📊 比較一覧表|一目でわかるLDO vs スイッチング

| 判断軸 | 🚰 LDO | ⚡ スイッチングレギュレータ |

|---|---|---|

| ①効率 | VOUT/VIN で決まる。 入出力差が大きいと非常に低い(20〜60%)。 入出力差が小さければ90%以上も可能。 |

入出力の電圧比に大きく依存しない。 典型値 85〜95%。 負荷が軽すぎると自己消費で効率低下。 |

| ②ノイズ | 非常に低い。スイッチングがないため出力リップルはμV〜数mVレベル。アナログ回路・ADC電源に最適。 | 高い。スイッチング周波数の整数倍のノイズが発生。出力リップルは数十mVレベル。EMI対策が必須。 |

| ③コスト | 安い。IC単価 数十〜数百円。外付け部品はコンデンサ2〜3個で済む。 | 高い。IC単価 数百〜数千円。インダクタ・ダイオード・コンデンサなど外付け部品が多い。 |

| ④実装サイズ | 小さい。IC+入出力コンデンサのみでOK。基板面積が限られる機器に有利。 | 大きい。インダクタが場所を取る。ただしモジュール型なら小型化可能。 |

| ⑤発熱 | 要注意。Ploss = (VIN-VOUT)×IOUT。電圧差×電流が大きいと深刻な発熱。 | 少ない。高効率のため損失が小さく、放熱設計が楽。 |

🔥 具体例で理解する|発熱量の計算

LDOの発熱がどれくらい深刻か、実際に数字で計算してみましょう。

Ploss = (12V - 3.3V) × 0.5A = 4.35W

これは「小さなハンダゴテ」くらいの発熱です。SOT-23パッケージのLDOでは絶対に耐えられません。放熱設計が破綻するか、IC自体が使用不可です。

一方、効率90%のスイッチングレギュレータなら:

Ploss = 3.3V × 0.5A × (1/0.9 - 1) = 0.18W

損失は約24分の1。この差が「LDOかスイッチングか」を決定づけます。

「(VIN - VOUT) × IOUT」が0.5Wを超えるなら、LDOは要注意。1Wを超えるなら、スイッチングレギュレータを第一候補にすべきです。

LDOが輝く場面 / スイッチングレギュレータが輝く場面

比較表だけでは「で、結局どの場面でどっちを使うの?」がピンと来ませんよね。ここでは具体的な使用シーンで整理します。

🚰 LDOを選ぶべき5つの場面

入出力の電圧差が小さい(1V以下)

例:3.6V → 3.3V の降圧。効率は 3.3/3.6 ≒ 92%。スイッチングと遜色ない効率が出せます。しかも部品点数が少なくコストも安い。LDOの独壇場です。

ADC・DAC・PLLなどノイズに超敏感な回路の電源

スイッチングノイズは数十mVのリップルを生みます。16bit ADCでは1LSB=数十μVの世界。LDOの低ノイズ(μVオーダー)でなければ精度が出ません。

出力電流が小さい(数十mA以下)

マイコンのスリープ電流やセンサーIC電源など。電流が小さければLDOの損失は無視できるレベルです。

基板面積が極端に限られる

ウェアラブル機器やセンサーモジュールなど。インダクタを置くスペースがない場合、LDO一択になることがあります。

スイッチングレギュレータの後段(ポストレギュレーション)

スイッチングで効率よく大まかに降圧 → LDOで低ノイズ・高精度に仕上げる。プロが最もよく使うハイブリッド構成です(後述)。

⚡ スイッチングレギュレータを選ぶべき5つの場面

入出力の電圧差が大きい

例:24V → 3.3V。LDOだと効率14%、損失 = 20.7V × IOUT。議論の余地なくスイッチングです。

出力電流が大きい(500mA以上)

モーター駆動回路、大規模FPGAの電源など。電流が大きいとLDOの損失が膨大になり、放熱が追いつきません。

バッテリー駆動で長寿命が求められる

IoTセンサー、ポータブル機器など。効率の差がバッテリー寿命に直結します。

昇圧が必要

3.3V → 5Vなど入力より高い電圧を作る場合。LDOは降圧専用なので、そもそも対応できません。昇圧型スイッチングレギュレータの出番です。

負電圧が必要

オペアンプ回路の-12V電源など。反転型スイッチングレギュレータでなければ実現できません。

「LDOは効率が低いからダメ」と一律に否定するのは間違いです。入出力差が0.3V程度なら、LDOの効率は90%を超えます。大切なのは「損失(=発熱量)が許容範囲に収まるか」で判断することです。

【フローチャート】もう迷わない!「LDO or スイッチング」判定マップ

ここまでの内容を1枚のフローチャートにまとめました。設計で迷ったとき、この図に当てはめれば答えが出ます。

🗺️ 判定フローチャート

(ADC / DAC / PLL / RF回路の電源)

(後段LDOも検討)

Q1→Q2→Q3→Q4の順に上から判定していくだけ。最初にYESになった時点で回答が確定します。迷ったらまず「損失計算」をしてQ2で判断するのが最も実用的です。

📋 よくある設計パターンと回答の早見表

| 設計パターン | VIN→VOUT | IOUT | 回答 |

|---|---|---|---|

| USB 5V → マイコン3.3V | 5V→3.3V | 100mA | 🚰 LDO 損失0.17W。問題なし |

| 車載12V → マイコン3.3V | 12V→3.3V | 300mA | ⚡ スイッチング 損失2.6W。LDOでは発熱地獄 |

| 24V → ADC用アナログ5V | 24V→5V | 50mA | ⚡+🚰 ハイブリッド SW→5.5V、LDO→5.0V |

| 3.3V → PLL用1.2V | 3.3V→1.2V | 50mA | 🚰 LDO 損失0.1W。ノイズ優先 |

| リチウム電池3.7V → LED 5V | 3.7V→5V | 200mA | ⚡ スイッチング 昇圧が必要。LDO不可 |

プロの必殺技「スイッチング+後段LDO」ハイブリッド構成

実はプロの設計者が最も多用するのは、「どちらか一方」ではなく「両方を組み合わせる」という手法です。

🏆 ハイブリッド構成とは?|「効率」と「低ノイズ」を両取りする

考え方はとてもシンプル。スイッチングレギュレータで大まかに降圧して「効率」を稼ぎ、後段のLDOで「ノイズを除去」するという2段構成です。

レギュレータ

効率90%で降圧

ノイズ除去

5.0V クリーン電源

📐 ハイブリッド構成のポイント3つ

後段LDOの目的は「ノイズ除去」であって「大きな降圧」ではありません。入出力差を0.3〜0.5V程度に設定すれば、LDOの損失は最小限に抑えられます。上記の例では、5.5V → 5.0V で差はたった0.5V。LDO部分の効率は 5.0/5.5 ≒ 91% です。

LDOが正常に動作するには、入力電圧が出力電圧+ドロップアウト電圧以上である必要があります。例えばドロップアウト電圧が300mVなら、5.0V出力には最低5.3Vが必要。スイッチングの出力電圧を設定するとき、このマージンを忘れないでください。

LDOがどれだけスイッチングノイズを除去できるかは、PSRR(Power Supply Rejection Ratio)で決まります。スイッチング周波数でのPSRRが40dB以上(1/100以下に減衰)あれば、十分なノイズ除去が期待できます。データシートの「PSRR vs 周波数」グラフを必ず確認しましょう。

LDOのPSRRは低周波(100Hz〜10kHz)では60〜80dBと優秀ですが、スイッチング周波数帯(数百kHz〜数MHz)では20〜40dBに低下します。「LDOを入れれば万能」ではありません。スイッチング側のフィルタ設計も同時に行うのがプロの仕事です。

【保存版】LDO vs スイッチング 設計チェックリスト

最後に、設計のたびに使えるチェックリストをまとめました。このリストを手元に置いておけば、「どっちにしよう?」で悩む時間がゼロになります。

✅ 7つのチェック項目

| No. | チェック項目 | 🚰 LDO向き | ⚡ スイッチング向き |

|---|---|---|---|

| 1 | 昇圧 or 負電圧が必要か? | 不可 | ✅ 対応可能 |

| 2 | 損失 (VIN-VOUT)×IOUT | 0.5W以下 | 1W以上 |

| 3 | ノイズ要求 | μV〜mVレベル | 数十mV許容 |

| 4 | 入出力電圧差 | 1V以下 | 2V以上 |

| 5 | 出力電流 | 数百mA以下 | 500mA以上 |

| 6 | コスト・部品点数の制約 | ✅ 安い・少ない | 高い・多い |

| 7 | バッテリー寿命の要求 | 入出力差が小さいなら可 | ✅ 高効率で有利 |

まとめ|「どっちを使う?」の答えは「損失」と「ノイズ」で決まる

- LDOは「蛇口を絞る」方式。エネルギーを捨てる(=熱になる)ため効率は入出力比で決まる

- スイッチングレギュレータは「ポンプ」方式。エネルギーを変換するため高効率だがノイズが出る

- 判断の第一歩は「(VIN-VOUT)×IOUT」の損失計算。1Wを超えたらスイッチングが第一候補

- ADC・PLL・RFなどノイズに敏感な回路にはLDOが必須

- プロは「スイッチング+後段LDO」のハイブリッド構成で効率と低ノイズを両立させる

- 「どちらかが正義」ではなく、条件に応じて使い分けるのが正解

電源設計は「地味だけど、ここが崩れると全てが崩れる」という、まさに縁の下の力持ち的な仕事です。LDOとスイッチングレギュレータの使い分けは、その第一歩。この記事のフローチャートとチェックリストを手元に置いて、自信を持って設計を進めてくださいね。

📚 次に読むべき記事

⚡ パワエレ設計・回路設計シリーズ

電源回路のスイッチ素子選定の基本。本記事と合わせて読めば電源設計力がアップ。

LDOの入出力コンデンサ選定にも直結する必須知識。

ESRの理解は電源設計のノイズ対策で必須。

スイッチングレギュレータ周辺の回路設計の全体像。

スイッチングレギュレータのサージ対策の基本。

スイッチング素子を正しく駆動するための回路設計。

降圧型スイッチングレギュレータ設計に必須の知識。

🔧 ノイズ対策・EMC設計シリーズ

スイッチングレギュレータのノイズ発生メカニズムを根本から理解。

基板レイアウトでノイズを激減させるテクニック。

スイッチングレギュレータ周りの基板設計のベストプラクティス。

LDOとスイッチングが混在する基板でのGND設計の鉄則。

ノイズの分類を理解すれば対策の方向性が明確になります。

スイッチングレギュレータが生む2種類のノイズを正しく分類。

EMC規格の全体像を把握して、設計初期から対策を織り込む。

電源ラインのノイズ対策の王道。

信号ラインのリンギング対策。LDO出力の安定化にも応用可能。

🔌 基板設計・部品選定シリーズ

パワエレ基板設計の入口。電源回路の基板は信号回路とルールが違います。

LDOなら2層でOK、スイッチングなら4層推奨の理由がわかります。

大電流ラインの基板設計に必須の知識。

電源設計で最も理解不足になりやすいGNDの本質。

LDOの出力コンデンサ配置にも通じるパスコンの原理。

スイッチングレギュレータの入出力コンデンサ設計に直結。

スイッチングノイズの根本原因を理解する名記事。

🔋 パワエレ基礎知識シリーズ

パワエレの全体像を掴みたい人はまずここから。

スイッチングレギュレータの整流素子の基本。

LDOの内部トランジスタ、スイッチングレギュレータのスイッチ素子の両方で使われるMOSFET。

電源回路で使われる半導体素子の全体像を一覧で把握。

絶縁型電源の設計に必須の知識。

電源設計の安全設計の根本思想。

絶縁型スイッチング電源で使われるフォトカプラの役割。

ノイズの基礎概念。LDOが「低ノイズ」と言われる理由を根本から理解。